# 65540 / 545

High Performance Flat Panel / CRT VGA Controllers

Data Sheet Revision 1.2

October 1995

#### CopyrightNotice

Copyright © 1995, Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies, Inc.

#### RestrictedRightsLegend

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### **Trademakknowledgement**

CHIPS Logotype, CHIPSlink, CHIPSPort, ELEAT, LeAPSet, NEAT, NEATsx, PEAK, PRINTGINE, SCAT, SuperMathDX, SuperState, and WINGINE are registered trademarks of Chips and Technologies, Incorporated.

CHIPSet, Super Math, WinPC, and XRAM Video Cache are trademarks of Chips and Technologies,Incorporated.

IBM® AT, XT, PS/2, Micro Channel, Personal System/2, Enhanced Graphics Adapter, Color Graphics Adapter, Video Graphics Adapter, IBM Color Display, and IBM Monochrome Display are trademarks of International Business Machines Corporation.

Hercules is a trademark of Hercules Computer Technology.

MS-DOS and Windows are trademarks of Microsoft Corporation.

MultiSync is a trademark of Nippon Electric Company (NEC).

Brooktree and RAMDAC are trademarks of Brooktree Corporation.

Inmos is a trademark of Inmos Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

VESA® is a registered trademark of Video Electronics Standards Association.

VL-Bus is a trademark of Video Electronics Standards Association.

All other trademarks are the property of their respective holders.

#### Disclaimer

This document is provided for the general information of the customer. Chips and Technologies, Inc., reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the data sheet. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

## 65540 / 545 High Performance Flat Panel / CRT VGA Controller

- Highly integrated design (flat panel / CRT VGA controller, RAMDAC, clock synthesizer)

- Multiple Bus Architecture Integrated Interface

- Local Bus (32-bit CPU Direct and VL)

- EISA/ISA (PC/AT) 16-bit Bus

- PCI Bus (65545)

- Flexible display memory configurations

- One 256Kx16 DRAM (512KB)

- Four 256Kx4 DRAMs (512KB)

- Two 256Kx16 DRAMs (1MB)

- Advanced frame buffer architecture uses available display memory, maximizing integration and minimizing chip count

- Integrated programmable linear address feature accelerates GUI performance

- Hardware windows acceleration (65545)

- 32-bit graphics engine

- System-to-screen and screen-to-screen BitBLT

- 3 operand ROP's

- Color expansion

- Optimized for Windows<sup>TM</sup> BitBLT format

- Hardware line drawing

- 64x64x2 hardware cursor

- Hardware pop-up icon (65545)

- 64x64 pixels by 4 colors

- 128x128 pixels by 2 colors

- High performance resulting from zero wait-state writes (write buffer) and minimum wait-state reads (internal asynchronous FIFO design)

- Mixed  $3.3V \pm 0.3V / 5.0V \pm 10\%$  Operation

- Interface to CHIPS' PC Video to display "live" video on flat panel displays

- Supports panel resolutions up to 1280 x 1024 resolution including 800x600 and 1024x768

- Supports non-interlaced CRT monitors with resolutions up to 1024 x 768 / 256 colors

- True-color and Hi-color display capability with flat panels and CRT monitors up to 640x480 resolution

- Direct interface to Color and Monochrome Dual Drive (DD) and Single Drive (SS) panels (supports 8, 9, 12, 15, 16, 18 and 24-bit data interfaces)

- Advanced power management features minimize power consumption during:

- Normal operation

- Standby (Sleep) modes

- Panel-Off Power-Saving Mode

- Flexible on-board Activity Timer facilitates ordered shut-down of the display system

- Power Sequencing control outputs regulate application of Bias voltage, +5V to the panel and +12 V to the inverter for backlight operation

- SMARTMAP<sup>TM</sup> intelligent color to gray scale conversion enhances text legibility

- Text enhancement feature improves white text contrast on flat panel displays

- Fully Compatible with IBM<sup>TM</sup> VGA

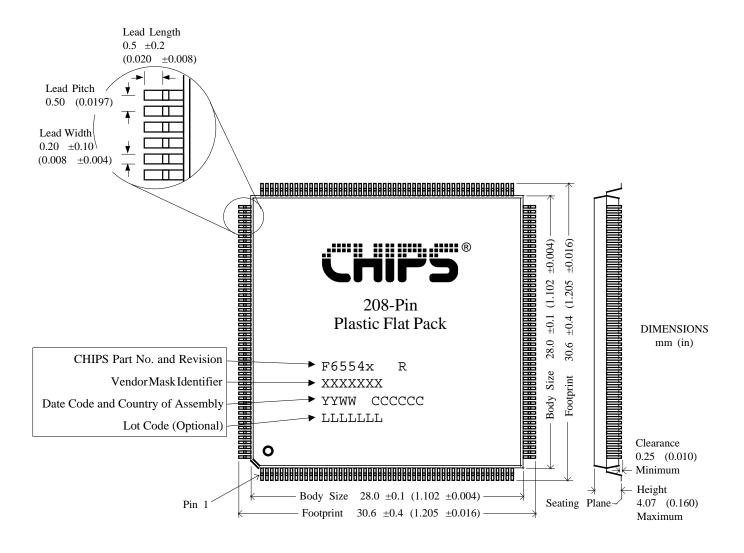

- EIAJ-standard 208-pin plastic flat pack

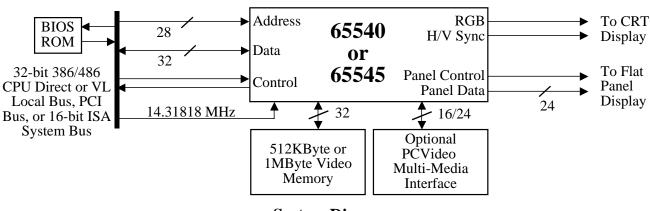

System Diagram

Revision 1.2 65540 / 545

## **Revision History**

| Revision | Date | By    | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1      | 9/94 | DH    | Added note: Refer to Electrical Specs for maximum clock frequencies in 'Supported Video Modes' table  Added note: Not all above resolutions can be supported at 3.3V and/or 5V Changed Mode 50 in Supported Video Modes-Extended Resolution Table from 16 to 16M  Reset column in Reset/Setup/Test/Standby/Panel-Off Mode table was incorrect. Now reads: "RESET#/Low/-/-/High/High"  Changed note for Pin List-Bus Interface: from "Drive=5V low drive and 3V high drive" to "IOL and IOH drive listed above indicates 5V low drive and 3.3V high drive (see also XR6C)"  Changed pin description: pin 25 LDEV# pin type "Out/OC" to "Out"  Changed Config Reg XR01 bits 2-1 VL-Bus description for pin 23=CRESET should read pin 23=RDYRTN#  Changed Ext Reg XR2D and XR2E to (CMPR Enabled) and (CMPR Disabled) and added note: "For DD panels without frame acceleration, the programmed value should be doubled"  Updated tables for "No FRC" and "2-Frame FRC"  Updated Flat Panel Timing "CD: 010" should read "CD: 001"  Updated Programming: FLM delay programmed in XR2C should be equal to: CRT blank time – FLM front porch – FLM width XR2D LP Delay (CMPR enabled) & XR2E LP Delay (CMPR disabled) Added note: "Can use external 14.31818 MHz oscillator into XTALI (203) with XTALO (204) as no connect"  Updated Elec Specs: changed "Max" under "Normal Operating Conditions" from 90 to 100; "memory clock is assumed to be 68 MHz not 65 MHz;" and "VL-Bus timing is compatible with VL-Bus Specification 2.0"  Added timing for VL-Bus LDEV#, 14.31818 MHz, DRAM R/M/W and PC-Video and modified timing for PCI Bus Frame |

| 1.2      | 7/95 | BB/MP | Clarified function of ACTI output. Updated Supported Video Modes table Updated I/O Map section Added 64310 to CHIPS VGA Product Family in Register Summary Updated Extension Registers table Updated XR33, XR6C, XR6F in the Extension Registers section Added Rset formula to CRT Panel Interface Circuit Updated Interface-Optrex DMF-50351NC-FW (640x480 Color STN-DD) LCD Panel Interface example Updated 65540/545 DC Characteristics in timing section Updated Local Bus Input Setup & Hold, Local Bus Output Valid, Local Bus Output Float Delay, VL-Bus LDEV#, CRT Output, Panel Output Timing diagrams Added 65545B2 specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## **Table of Contents**

| Section Section                                                | <b>Page</b> | <b>Section</b>                                                | <u>Page</u> |

|----------------------------------------------------------------|-------------|---------------------------------------------------------------|-------------|

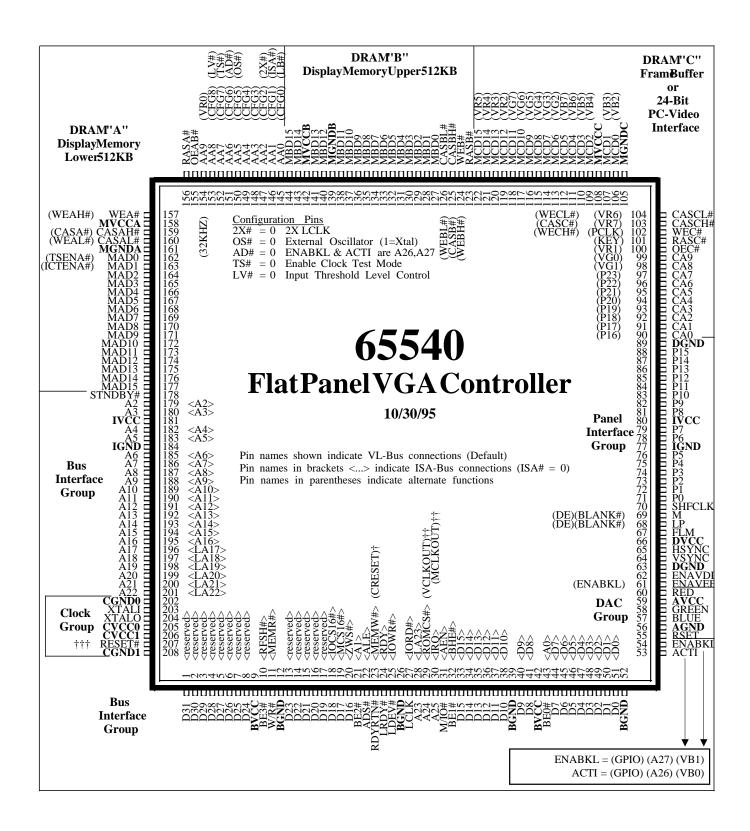

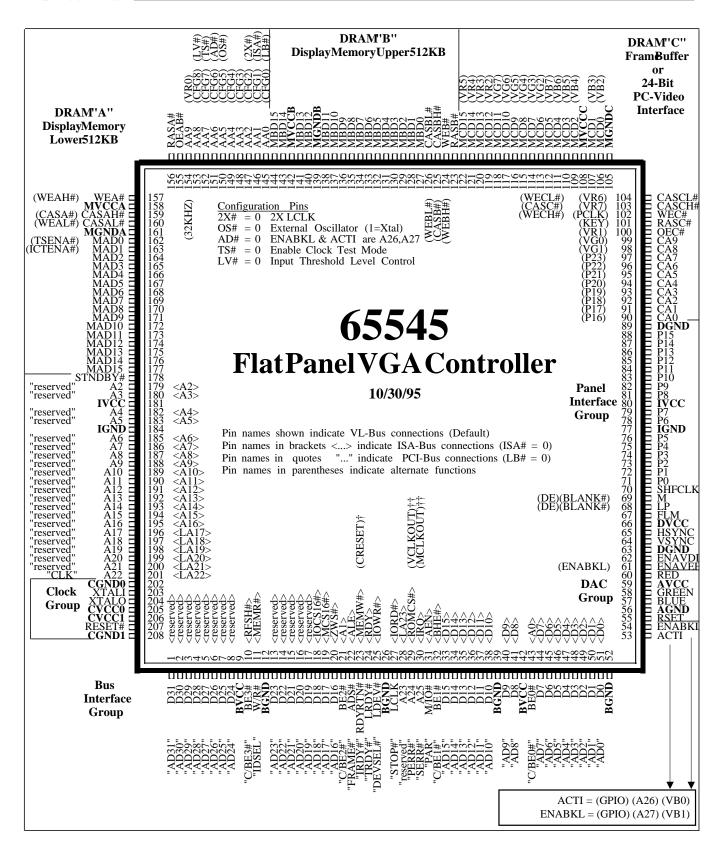

| Introduction / Overview                                        | 7           | Pinouts (65540)                                               |             |

| Minimum Chip Count / Board Space                               | 8           | Pinouts (65545)                                               | 24          |

| Display Memory Interface                                       |             | Pin Diagram (65540)                                           | 23          |

| CPU Bus Interface                                              |             | Pin Diagram (65545)                                           | 24          |

| High Performance Features                                      | 10          | Pin Lists                                                     | 25          |

| 65545 Acceleration                                             | 10          | Pin Descriptions - ISA/VL-Bus Interface                       |             |

| 65545 Hardware Cursor                                          | 10          | Pin Descriptions - PCI Bus Interface                          | 31          |

| PC Video / Overlay Support                                     |             | (65545 only)                                                  | 34          |

| Display Interface                                              | 11          | Pin Descriptions - Display Memory                             | -           |

| Flat Panel Displays                                            |             | Pin Descriptions - Flat Panel Interface                       | 39          |

| Panel Power Sequencing                                         |             | Pin Descriptions - CRT and Clock Interface                    |             |

| CRT Displays                                                   | 11          | Pin Descriptions - Power / Gnd / Standby                      | 42          |

| Simultaneous Flat Panel / CRT Display                          | 14          | Thi Descriptions Tower / Sha / Standoy                        | 12          |

| Display Enhancement Features                                   | 14          | Register and Port Address Summaries                           | 43          |

| "True-Gray" Gray Scale Algorithm                               |             | -                                                             |             |

| RGB Color to Gray Scale Reduction                              |             | I/O Map                                                       | 43          |

| SmartMap <sup>TM</sup>                                         |             | CGA, MDA, and Hercules Registers                              |             |

| Text Enhancement                                               |             | EGA Registers                                                 | 44          |

|                                                                |             | VGA Registers                                                 | 44          |

| Vertical and Horizontal Compensation Advanced Power Management |             | VGA Indexed Registers                                         | 45          |

| Normal Operating Mode                                          | 16          | Extension Registers                                           | 46          |

| Mixed 3.3V and 5V Operation                                    | 16          | 32-Bit Registers (65545)                                      | 49          |

| Panel Off Mode                                                 | 16          | PCI Configuration Registers (65545)                           | 50          |

| Standby Mode                                                   | 16          |                                                               |             |

| CRT Power Management (DPMS)                                    |             | Register Descriptions                                         | 51          |

| CPU Activity Indicator / Timer                                 | 17          | Global Control (Setup) Registers                              | 53          |

| Full Compatibility                                             | 17          |                                                               |             |

| Write Protection                                               | 17          | PCI Configuration RegistersGeneral Control & Status Registers | 59          |

| Extension Registers                                            |             | CGA / Hercules Registers                                      | 61          |

| Panel Interface Registers                                      |             | Sequencer Registers                                           | 63          |

| Alternate Panel Timing Registers                               |             | CRT Controller Registers                                      | 67          |

| Context Switching                                              |             | Graphics Controller Registers                                 | 81          |

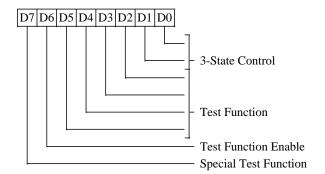

| Reset, Setup, and Test Modes                                   | 18          | Attribute Controller and                                      | 01          |

| Reset Mode                                                     | 18          | VGA Color Palette Registers                                   | 89          |

| Setup Mode                                                     |             | Extension Registers                                           | 95          |

| Tri-State Mode                                                 |             | 32-Bit Registers (65545 only)                                 |             |

| ICT (In-Circuit-Test) Mode                                     | 18          | 32-Dit Registers (033+3 only)                                 | 133         |

| Chip Architecture                                              | 19          |                                                               |             |

| Sequencer                                                      |             |                                                               |             |

| CRT Controller                                                 | -           |                                                               |             |

| Graphics Controller                                            |             |                                                               |             |

| Attribute Controller                                           |             |                                                               |             |

| VGA / Color Palette DAC                                        |             |                                                               |             |

| Clock Synthesizers                                             |             |                                                               |             |

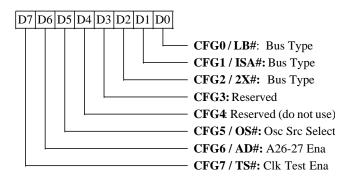

| Configuration Inputs                                           | 21          |                                                               |             |

| Configuration InputsVirtual Switch Register                    | 21          |                                                               |             |

| Light Pen Registers                                            | 21          |                                                               |             |

| Light Pen RegistersBIOS ROM Interface                          | 21          |                                                               |             |

| Package                                                        | 21          |                                                               |             |

| Application Schematics                                         |             |                                                               |             |

| 1 ppiication benefitation                                      |             |                                                               |             |

## **Table of Contents**

| Section                                           | <b>Page</b> | Section                                | Page              |

|---------------------------------------------------|-------------|----------------------------------------|-------------------|

| Functional Description                            | 165         | Programming and Parameters             | 195               |

| System Interface                                  | 165         | General Programming Hints              | 195               |

| Functional Blocks                                 | 165         | Parameters for Initial Boot            | 197               |

| Bus Interface                                     |             | Parameters for Emulation Modes         |                   |

| ISA Interface                                     |             | Parameters for Monochrome LCD Panels   | 170               |

| VL-Bus Interface                                  |             | (Panel Mode Only)                      | 199               |

|                                                   |             | Parameters for Monochrome LCD Panels   | 1))               |

| Direct Processor Interface                        |             |                                        | 200               |

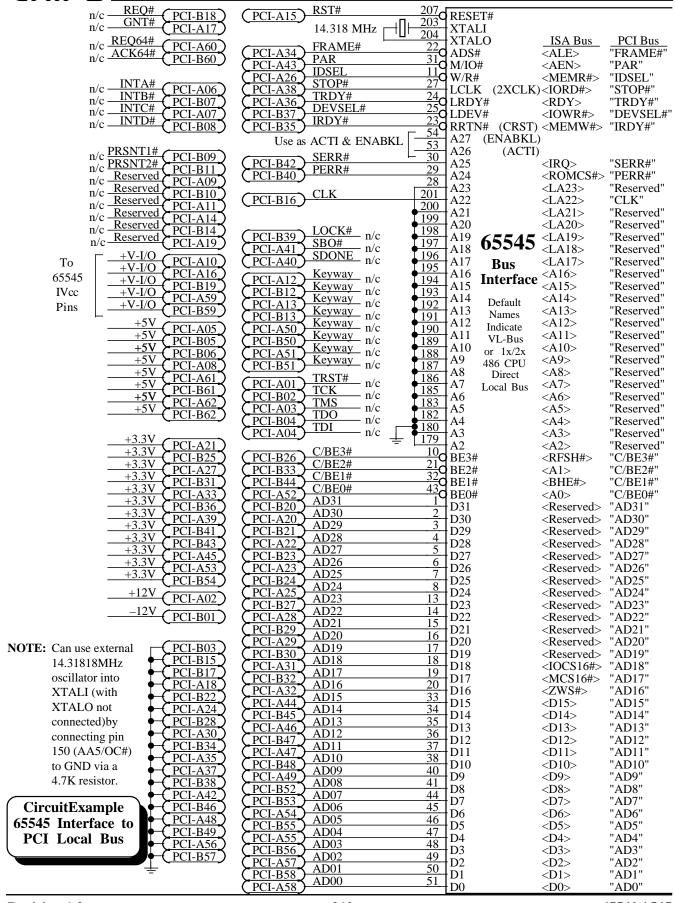

| PCI Interface                                     | 103         | (Simultaneous Mode Display)            | 200               |

| Display Memory Interface                          | 166         | Parameters for Color TFT Panels        | 201               |

| Memory Architecture                               | 166         | (Panel Mode Only)                      | 201               |

| Memory Chip Requirements                          | 166         | Parameters for Color TFT Panels        | 202               |

|                                                   |             | (Simultaneous Mode Display)            | 202               |

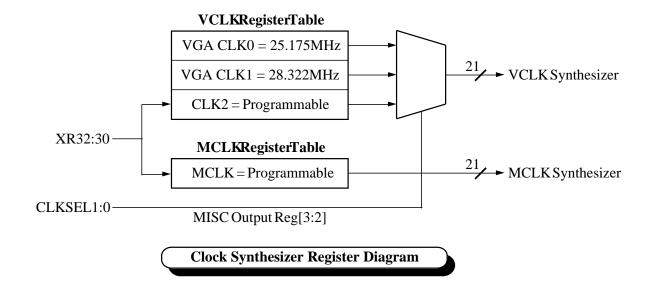

| Clock Synthesizer                                 |             | Parameters for Color STN SS Panels     | 202               |

| MCLK Operation                                    |             | (Panel & Simultaneous Mode Display)    | 203               |

| VCLK Operation                                    | 168         | Parameters for Color STN SS Panels     |                   |

| Programming the Clock Synthesizer.                |             | (Extended 4-bit Pack)                  | 204               |

| Programming Constraints                           |             | Parameters for Color STN DD Panels     |                   |

| Programming Example                               |             | (Panel & Simultaneous Mode Display)    | 205               |

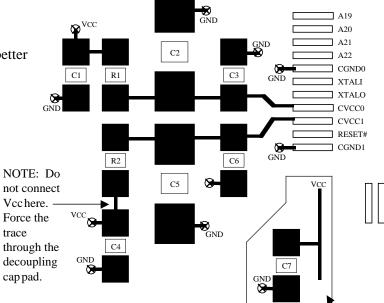

| PCB Layout Considerations                         | 169         | Parameters for Plasma Panels           | 206               |

| •                                                 |             | Parameters for EL Panels               | 207               |

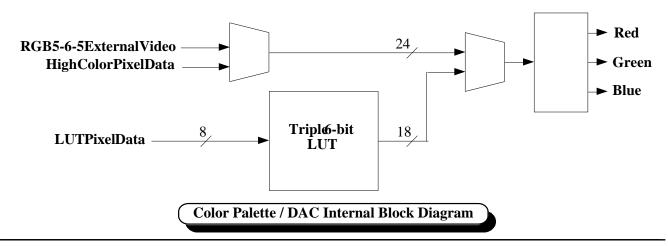

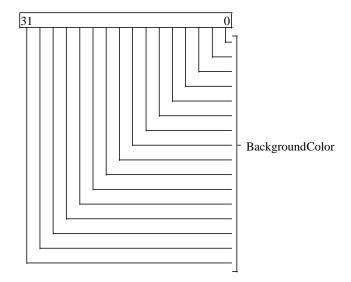

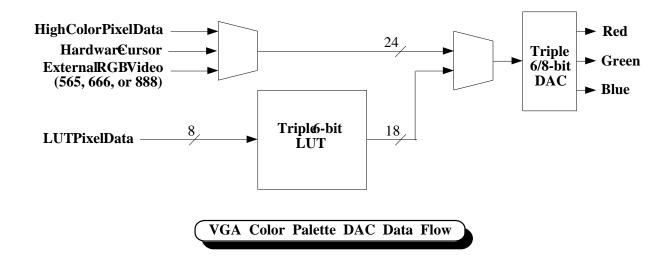

| VGA Color Palette DAC                             | 170         |                                        |                   |

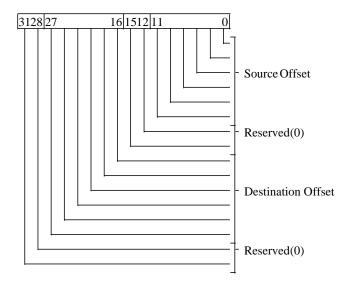

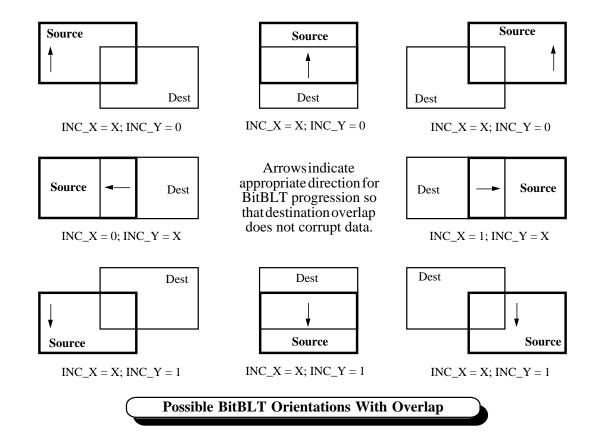

| BitBLT Engine (65545 only)                        | 171         | Application Schematics                 | 209               |

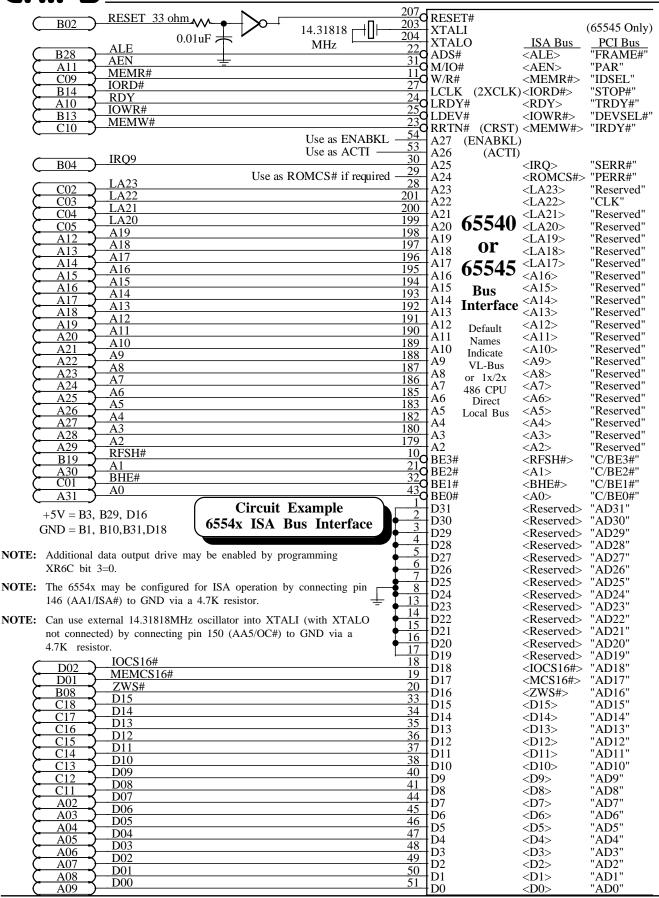

| Bit Block Transfer                                |             | System Bus Interface                   | 210               |

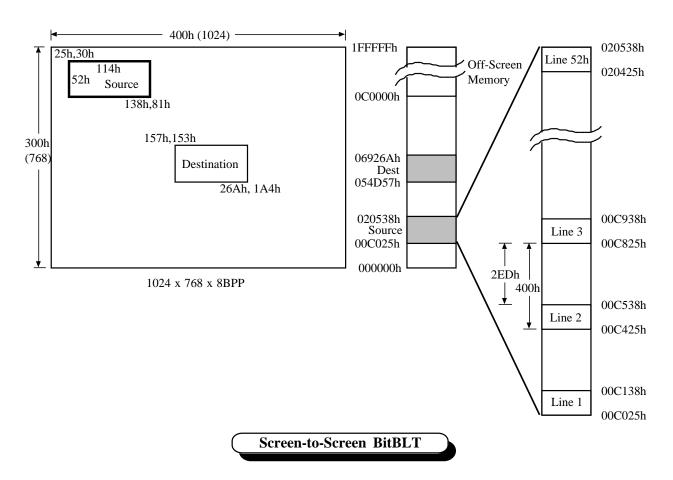

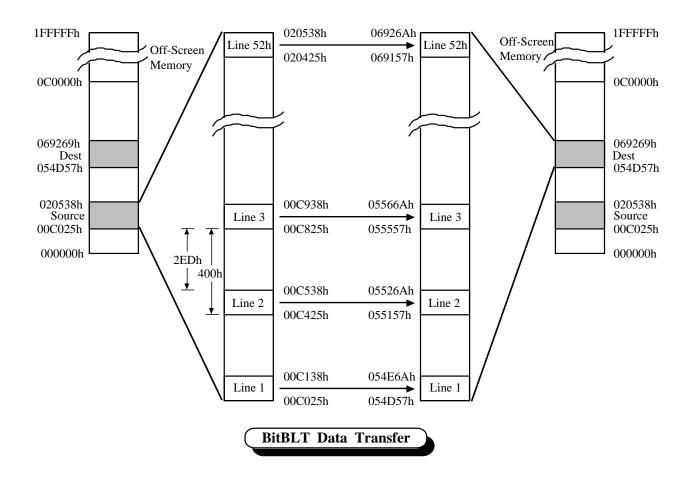

| Sample Screen-to-Screen Transfer                  | 172         | VL-Bus / 486 CPU Local Bus Interface   | $\frac{211}{211}$ |

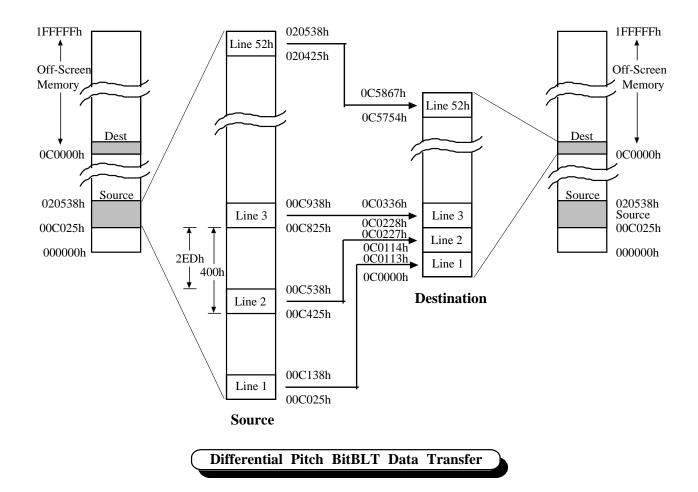

| Compressed Screen-to-Screen Transfer .            |             | PCI Local Bus Interface                |                   |

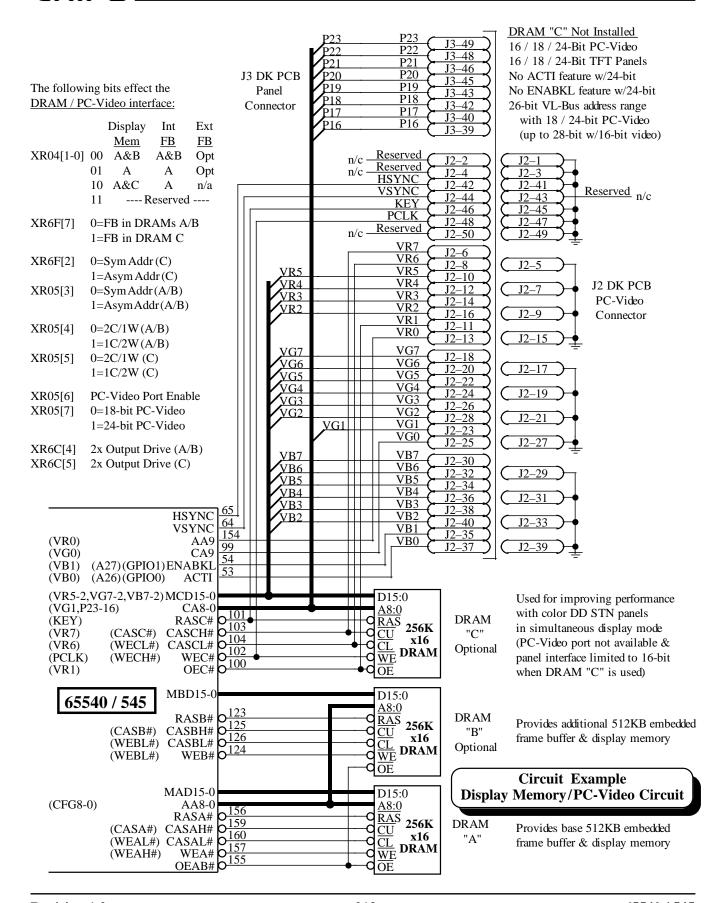

| System-to-Screen BitBLTs                          | 175         | Display Memory / PC Video Interface    |                   |

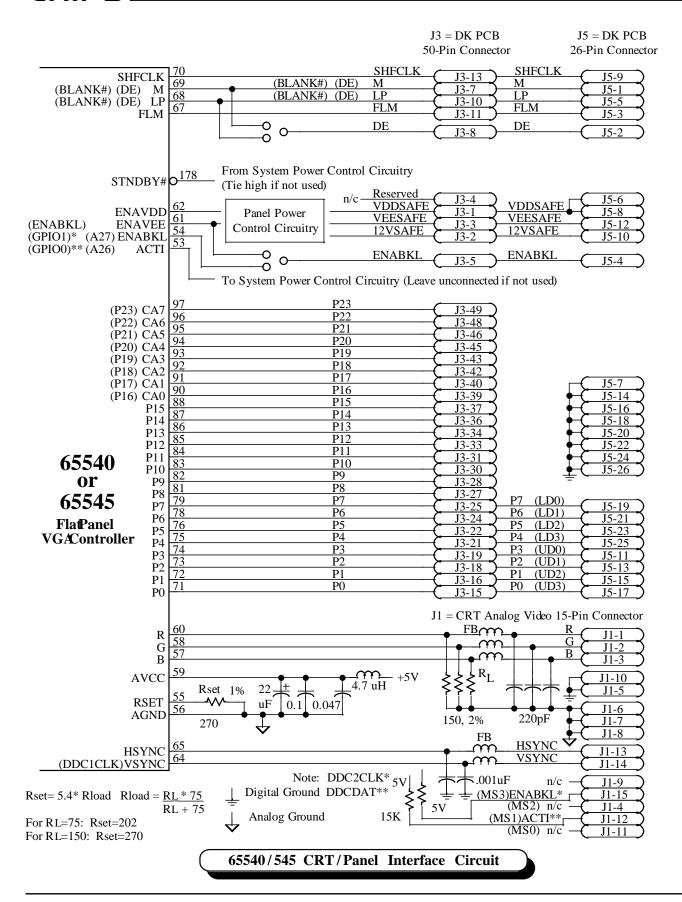

| •                                                 |             | CRT / Panel Interface                  | $\frac{213}{214}$ |

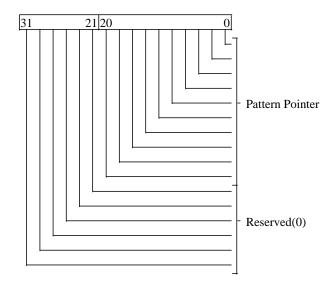

| Hardware Cursor (65545 only)                      |             | CKT / Tanci interface                  | 21 <del>4</del>   |

| Programming                                       |             | Danal Interface Examples               | 215               |

| Cursor Data Array Format & Layout                 | 177         | Panel Interface Examples               | 213               |

| Display Mem Base Addr Formation .                 |             | Electrical Considerations              | 241               |

| VGA Controller Programming                        | 178         | Electrical Specifications              | 241               |

| Copying Cursor Data to Disp Mem                   |             | Absolute Maximum Conditions            | 241               |

| Setting Position, Type, & Base Addr               | 178         | Normal Operating Conditions            |                   |

|                                                   |             | DAC Characteristics                    | 241               |

| Flat Panel Timing                                 | 179         | DC Characteristics                     |                   |

| Overview                                          |             | DC Drive Characteristics               |                   |

|                                                   |             | AC Test Conditions                     | 2/13              |

| Panel Size                                        |             | AC Characteristics                     | 273               |

| Panel Type                                        | 179         | Reference Clock Timing                 | 2/13              |

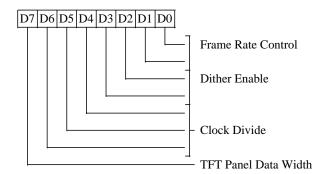

| TFT Panel Data Width                              | 1/9         | Clock Concretor Timing                 | 243               |

| Display Quality Settings Frame Rate Control (FRC) | 180         | Clock Generator Timing                 | 244               |

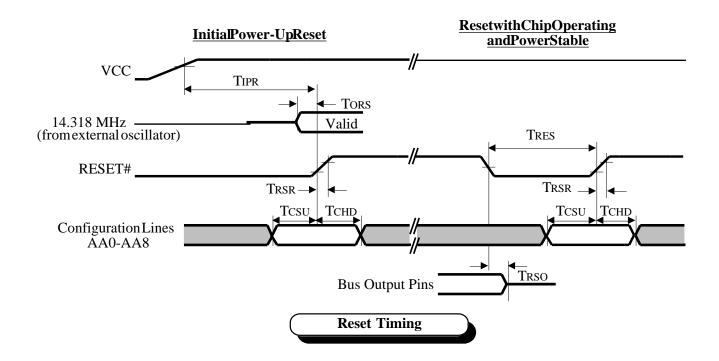

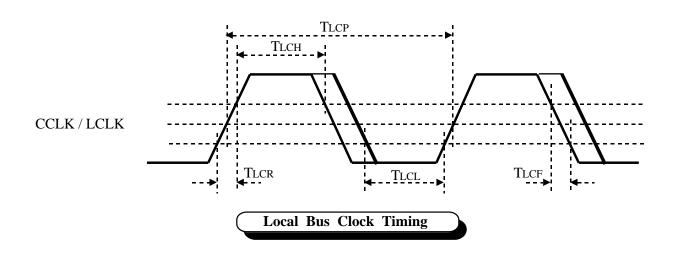

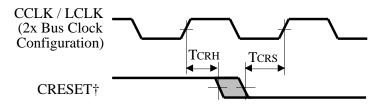

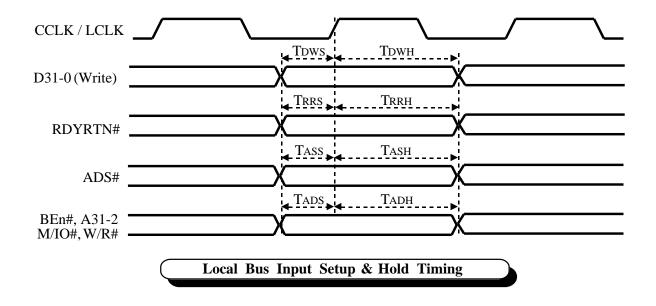

| Frame Rate Control (FRC)                          | 180         | Reset Timing                           | 243               |

| Dither                                            | 180         | Bus Timing                             | 240               |

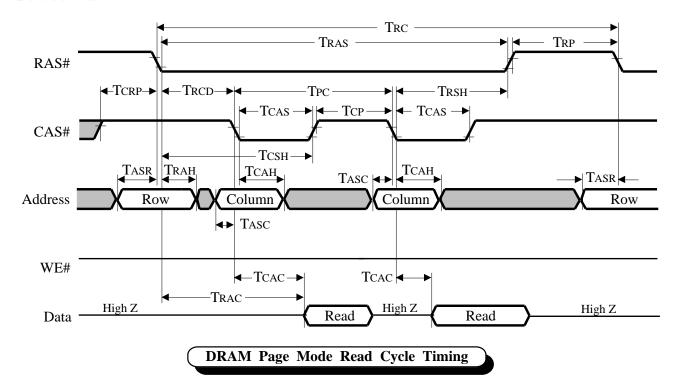

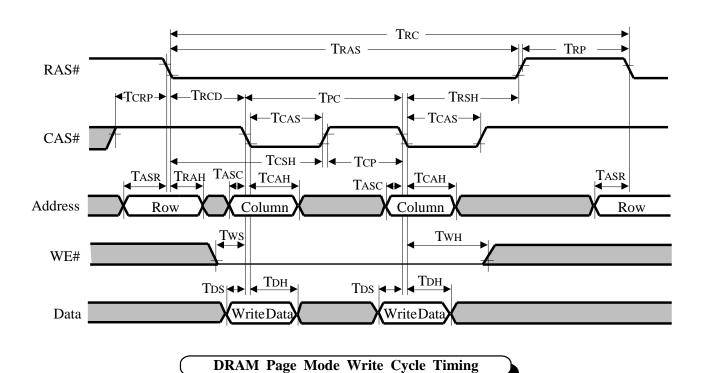

| M Signal Timing                                   | 180         | DRAM Timing                            | 254               |

| Gray / Color Levels                               | 180         | CRT Output Timing                      | 258               |

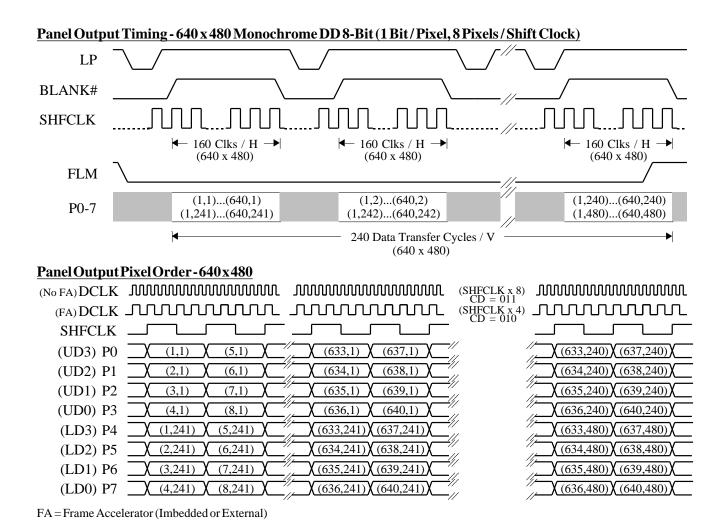

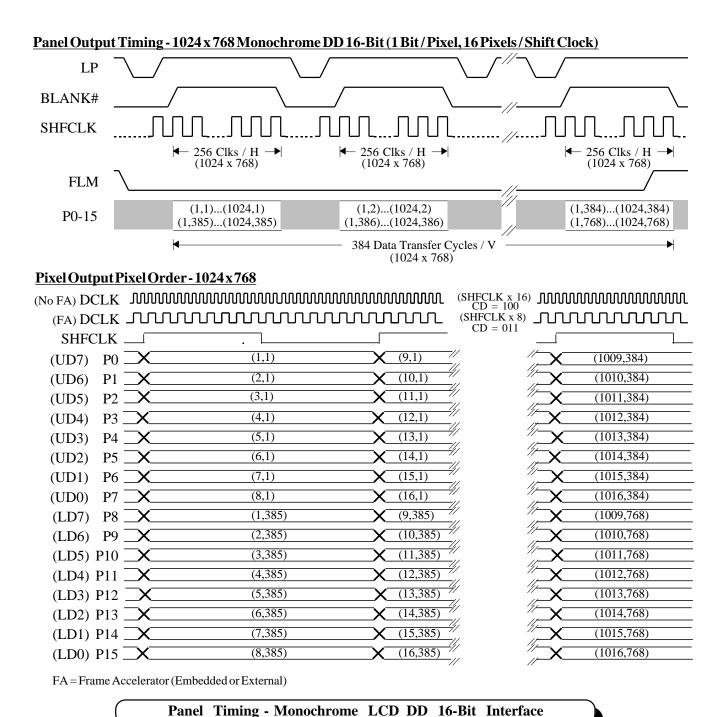

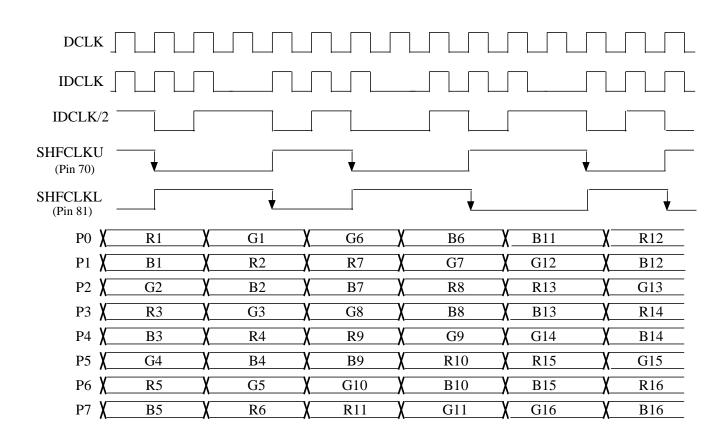

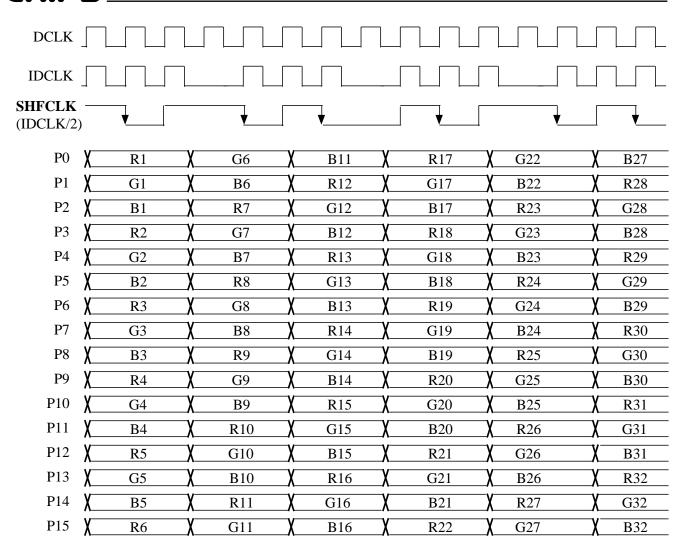

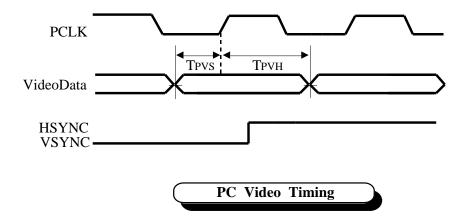

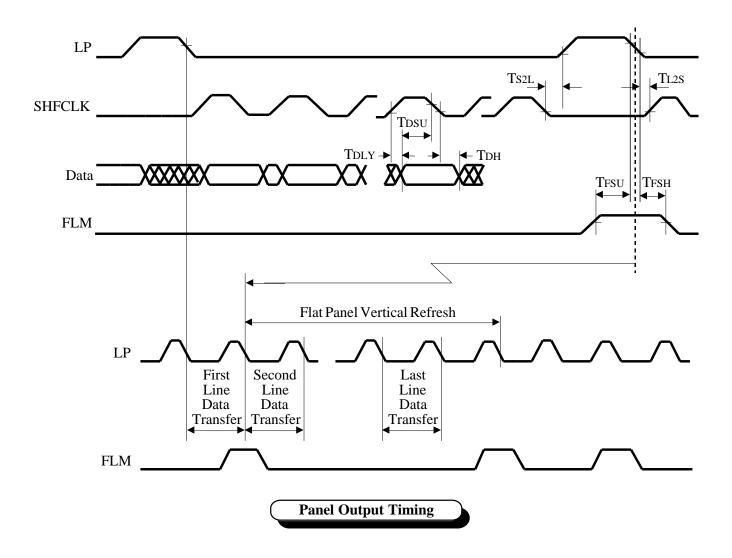

| Pixels Per Shift Clock                            | 181         | PC Video Timing<br>Panel Output Timing | 258               |

| Color STN Pixel Packing                           | 182         | Panel Output Timing                    | 259               |

| Output Signal Timing                              |             |                                        |                   |

| LP Signal Timing                                  |             | Mechanical Specifications              | 261               |

| FLM Output Signal Timing                          | 183         | Plastic 208-PFP Package Dimensions     | 261               |

| Blank#/DE Output Signal Timing                    |             | 1 lastic 200-FTF Fackage Difficusions  | ∠01               |

| Shift Clock Output Signal Timing                  | 183         |                                        |                   |

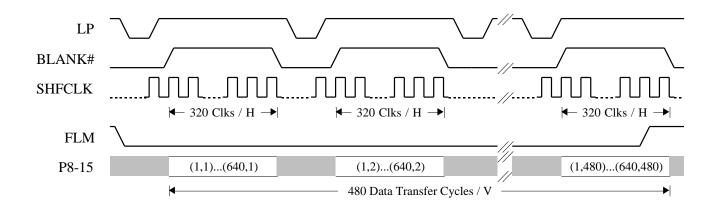

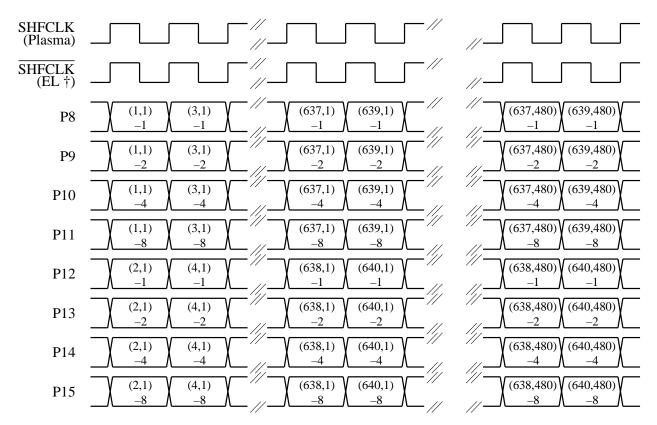

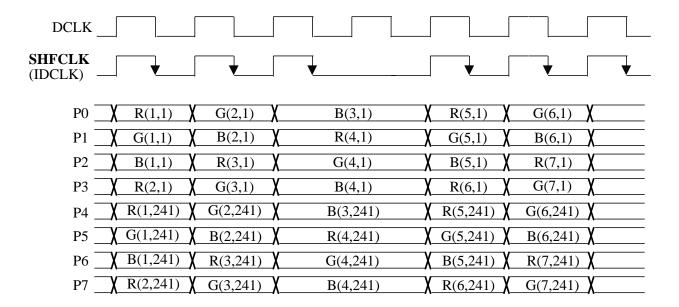

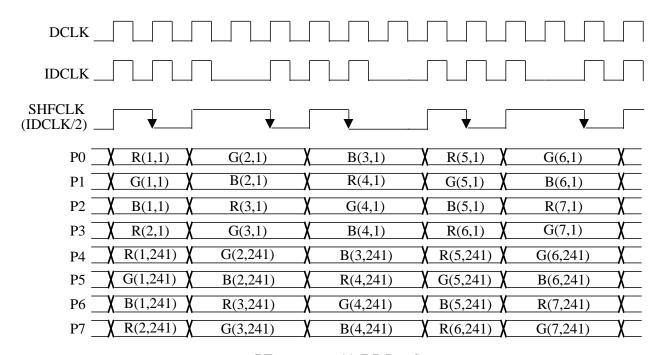

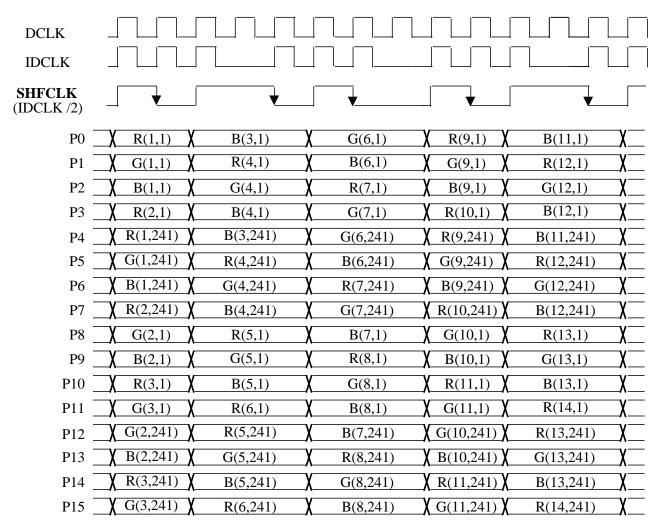

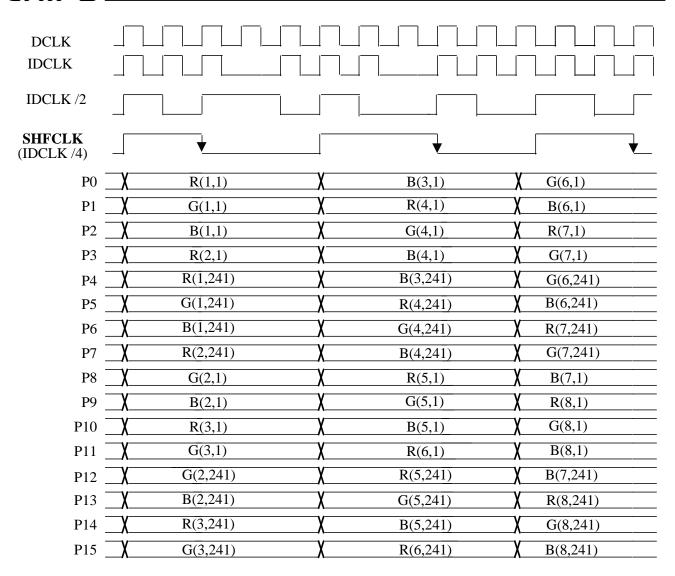

| Pixel Timing Sequence Diagrams                    | 183         |                                        |                   |

|                                                   |             |                                        |                   |

## **List of Tables**

| <u>Table</u>                                | <u>Page</u> | <b>Table</b>                        | Page |

|---------------------------------------------|-------------|-------------------------------------|------|

| Feature Differences                         | 7           | Parameters - Initial Boot           | 197  |

| Display Capabilities                        | 9           | Parameters - Emulation Modes        |      |

| Supported Video Modes - VGA                 | 12          | Parameters - Monochrome LCD-DD      |      |

| Supported Video Modes - Extended            | 13          | Panel Mode Only                     | 199  |

| Supported Video Modes - High Refresh        | 13          | Simultaneous Mode Display           |      |

| Vcc Pin to Interface Pin Correspondence     | 16          | Parameters - Color TFT LCD          | 200  |

| Reset/Setup/Test/Standby/Panel-Off Modes    | 18          | Panel Mode Only                     | 201  |

|                                             | 21          | Simultaneous Mode Display           |      |

| Configuration Pin Summary                   | <i>L</i> 1  |                                     | 202  |

| Pin List                                    | 25          | Parameters - Color STN-SS LCD       | 202  |

| Pin Descriptions                            | 31          | Panel & Simultaneous Mode Display   | 203  |

| 2 iii 2 00011p010110                        | 0.1         | Parameters - Color STN-DD LCD       | 20.4 |

| Standby Mode Panel Output Signal Status     | 41          | 8-bit Interface Extended 4-bit Pack |      |

| Standby Mode Memory Output Signal Status.   | 41          | 16-bit Interface (with FA)          |      |

| Standby Mode Bus Output Signal Status       | 42          | Parameters - Monochrome Plasma      |      |

|                                             | 43          | Parameters - Monochrome EL          | 207  |

| I/O Map                                     | 44          |                                     |      |

| Register Summary - CGA/MDA/Herc Modes       |             | Panel Interface Examples Summary    | 215  |

| Register Summary - EGA Mode                 | 44          | DK Board Connector Summary          |      |

| Register Summary - VGA Mode                 | 44          | ·                                   |      |

| Register Summary - Indexed Registers        | 45          | Absolute Maximum Conditions         | 241  |

| Register Summary - Extension Registers      | 46          | Normal Operating Conditions         |      |

| Register Summary - 32-Bit Registers (65545) | 49          | DAC Characteristics                 |      |

| Register Summary - PCI Confg Regs (65545)   | 50          | DC Characteristics                  |      |

| Register List - Setup Registers             | 53          | DC Drive Characteristics            |      |

|                                             | 55<br>55    | AC Test Conditions                  |      |

| Register List - PCI Configuration           |             | AC Timing Characteristics           |      |

| Register List - General Control & Status    | 59          | Reference Clock                     |      |

| Register List - CGA / Hercules Registers    | 61          | Clock Generator                     |      |

| Register List - Sequencer                   | 63          |                                     |      |

| Register List - CRT Controller              | 67          | Reset                               |      |

| Register List - Graphics Controller         | 81          | Local Bus Clock                     |      |

| Register List - Attribute Controller        |             | Local Bus Input Setup & Hold        |      |

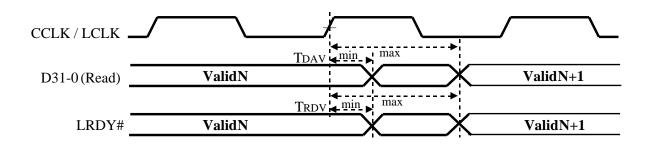

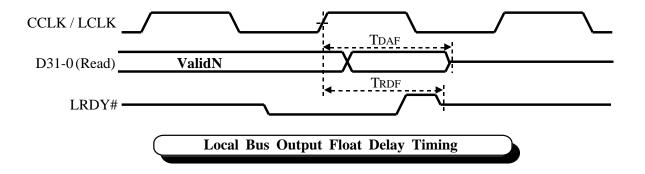

| and VGA Color Palette                       | 89          | Local Bus Output Valid              | 248  |

| Register List - Extension Registers         | 95          | Local Bus Float Delay               | 248  |

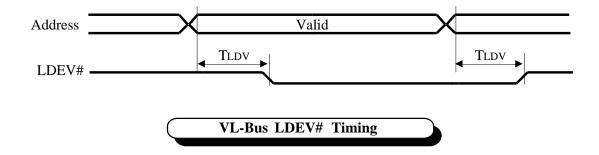

| Register List - 32-Bit Registers (65545)    | 155         | VL-Bus LDEV#                        |      |

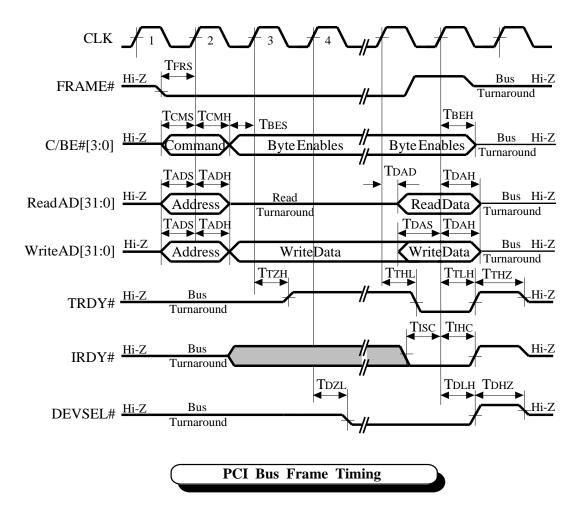

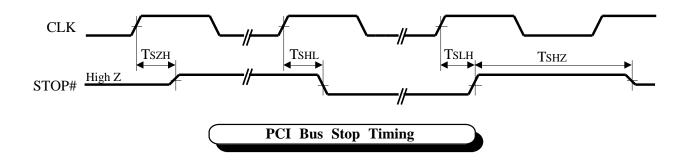

|                                             |             | PCI Bus Frame                       |      |

| DRAM Speed vs. Memory Clock Frequency.      | 166         | PCI Bus Stop                        |      |

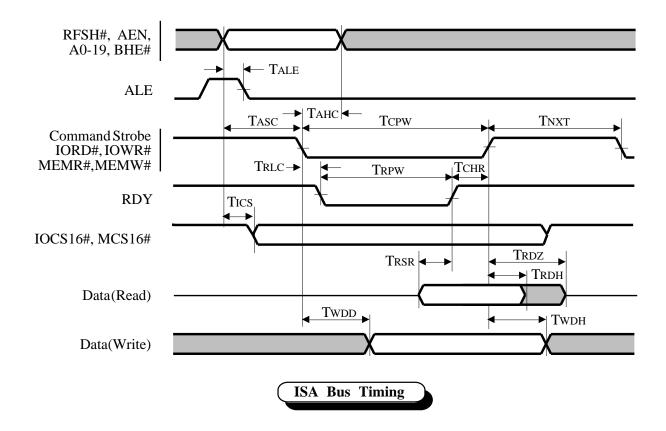

|                                             |             | ISA Bus                             |      |

|                                             |             | DRAM Read / Write                   | 254  |

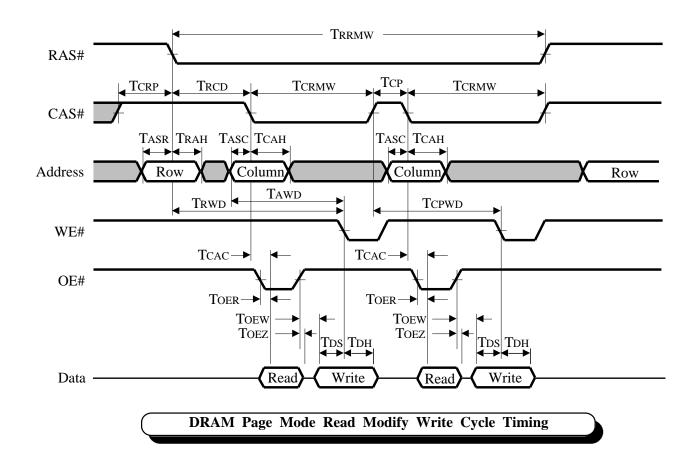

|                                             |             | DRAM Read / Modify / Write          | 256  |

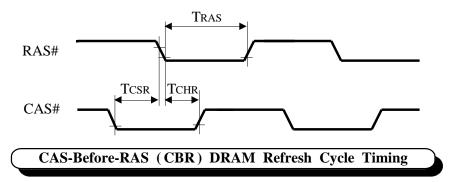

|                                             |             | DRAM CBR-Refresh                    |      |

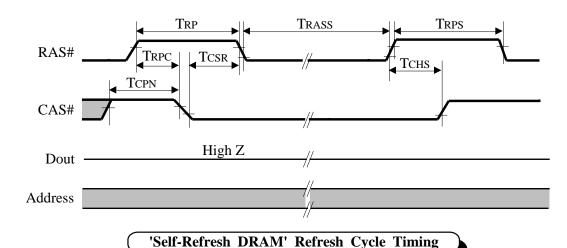

|                                             |             | DRAM Self-Refresh                   |      |

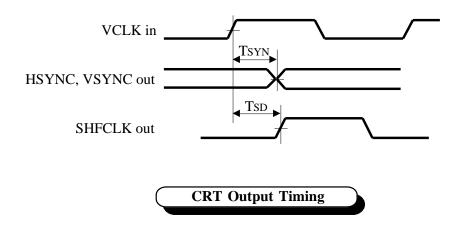

|                                             |             | CRT Output                          |      |

|                                             |             | PC Video                            |      |

|                                             |             | Panel Output                        |      |

## **List of Figures**

| <u>Figure</u>                                                                                                                                                                                                                                                                                    | <b>Page</b>                                          | <u>Figure</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

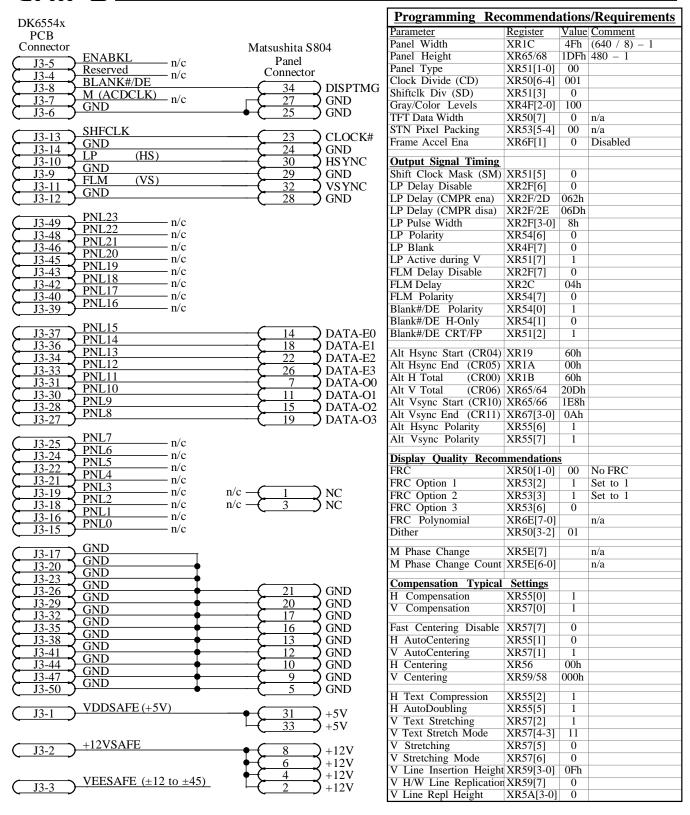

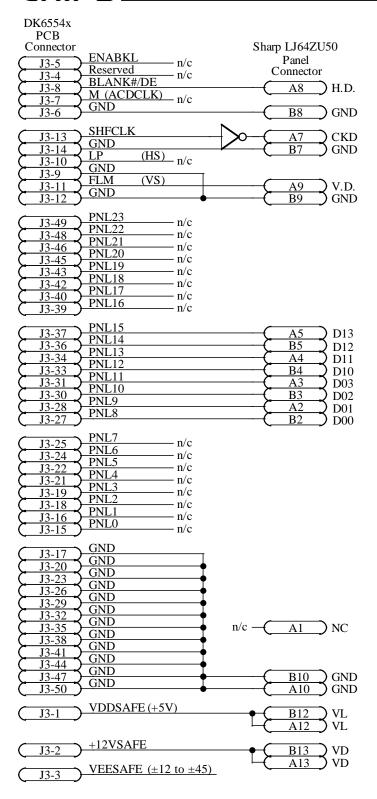

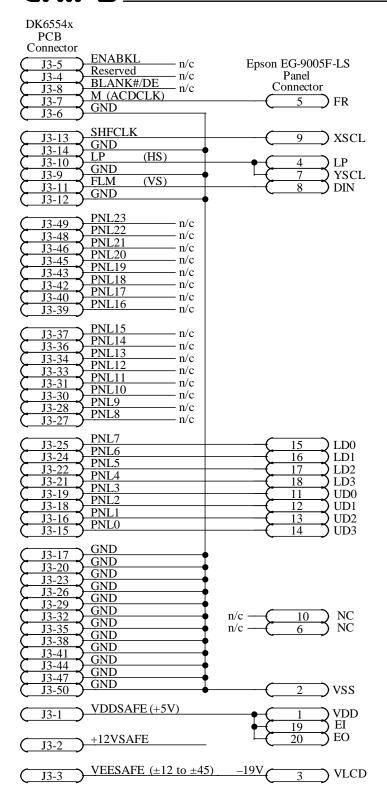

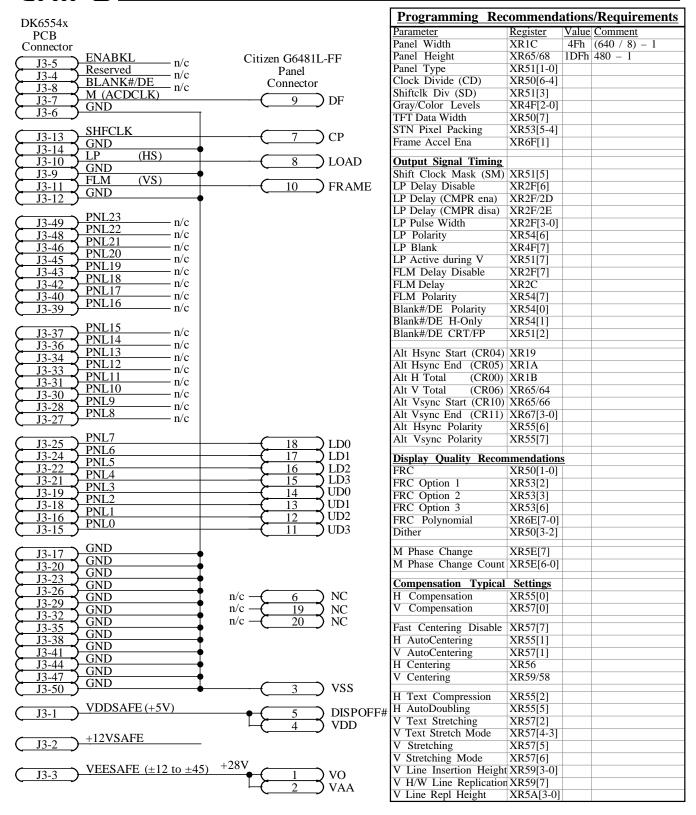

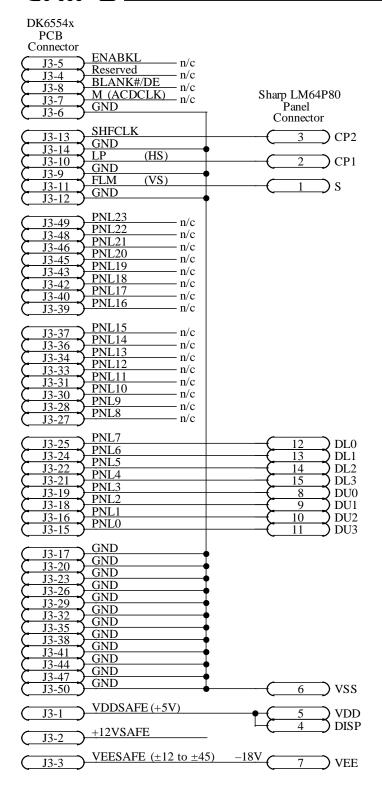

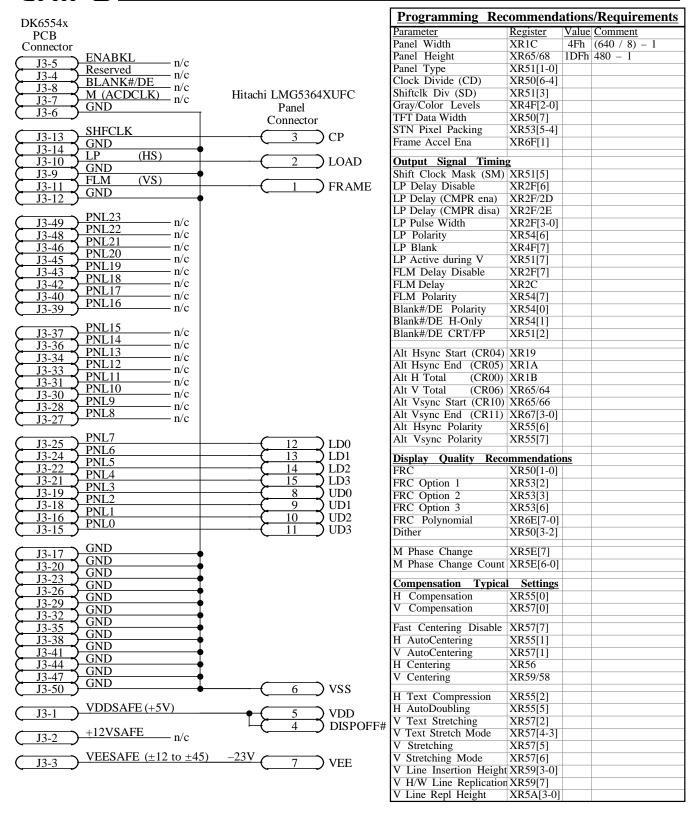

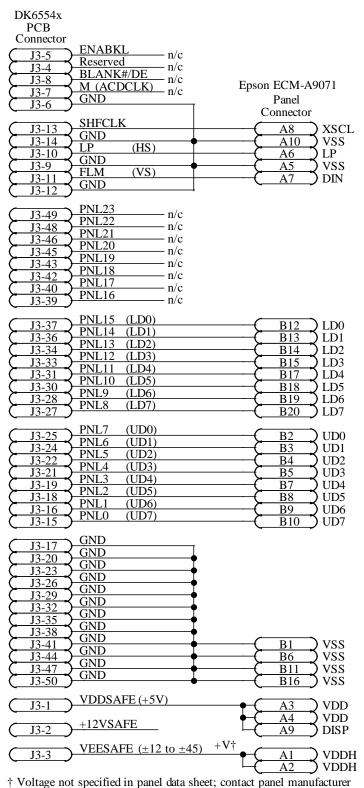

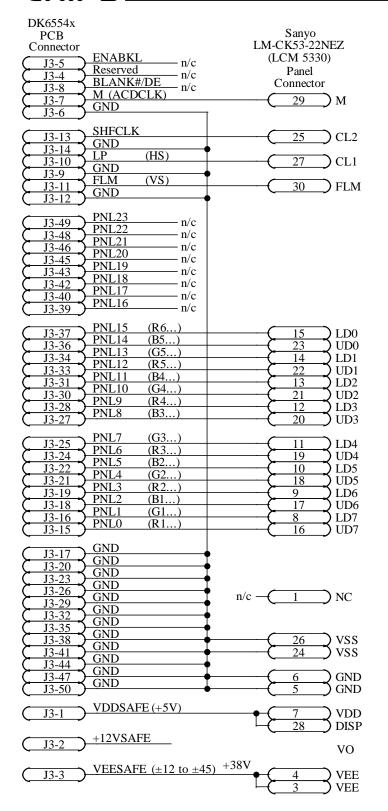

| System Diagram                                                                                                                                                                                                                                                                                   | 1<br>11<br>19<br>20<br>23                            | Flat Panel Interface Schematics  Plasma-16 - Matsushita S804  EL-16 - Sharp LJ64ZU50  Mono DD - Epson EG9005F-LS  Mono DD - Citizen G6481L-FF                                                                                                                                                                                                                                                                                                                  | 217<br>218<br>219                                                                              |

| Pinouts (65545)                                                                                                                                                                                                                                                                                  | 25                                                   | Mono DD - Sharp LM64P80<br>Mono DD - Sanyo LCM6494-24NTK<br>Mono DD - Hitachi LMG5364XUFC<br>Mono DD - Sanyo LCM-5491-24NAK                                                                                                                                                                                                                                                                                                                                    | 222<br>223<br>224                                                                              |

| Clock Synthesizer Register Structure Clock Synthesizer PLL Block Diagram Clock Filter Circuit Clock Power / Ground Layout Example VGA Color Palette DAC Data Flow Possible BitBLT Orientations With Overlap Screen-to-Screen BitBLT BitBLT Data Transfer Differential Pitch BitBLT Data Transfer | 167<br>169<br>169<br>170<br>171<br>172<br>173        | Mono DD - Epson ECM-A9071  Color TFT - Hitachi TM26D50VC2AA  Color TFT - Sharp LQ9D011  Color TFT - Toshiba LTM-09C015-1  Color TFT - Sharp LQ10D311  Color TFT - Sharp LQ10DX01  Color STN SS - Sanyo LM-CK53-22NEZ  Color STN SS - Sanyo LCM5327-24NAK.  Color STN SS - Sharp LM64C031                                                                                                                                                                       | 226<br>227<br>228<br>229<br>230<br>231<br>232                                                  |

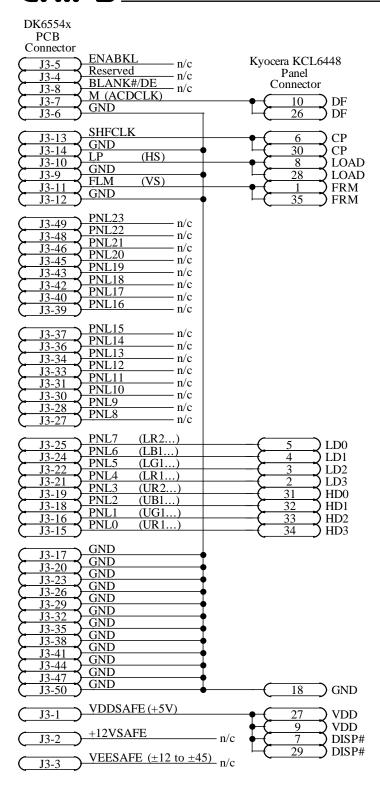

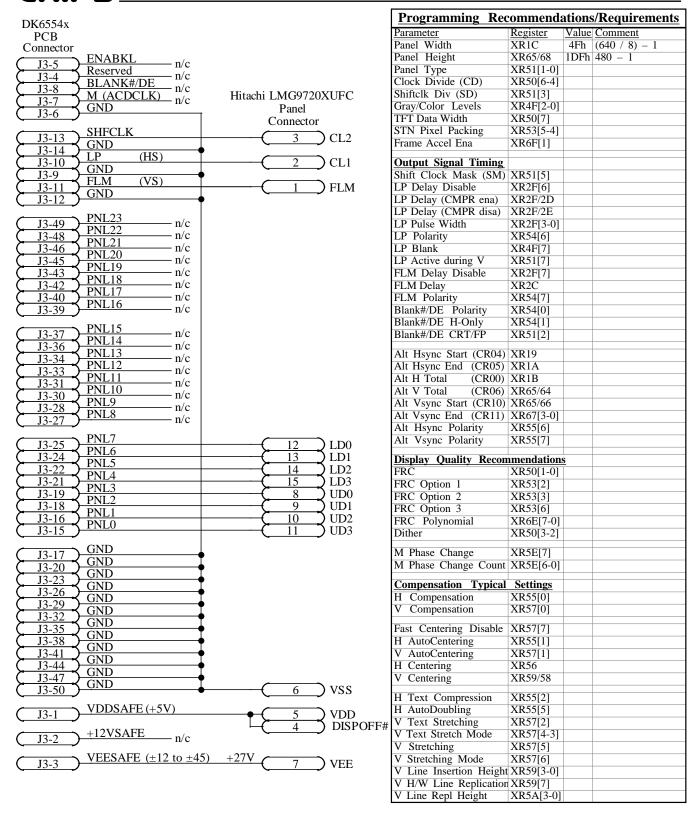

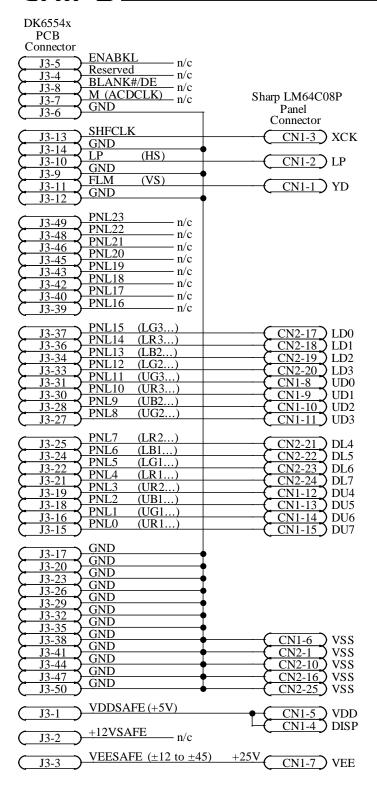

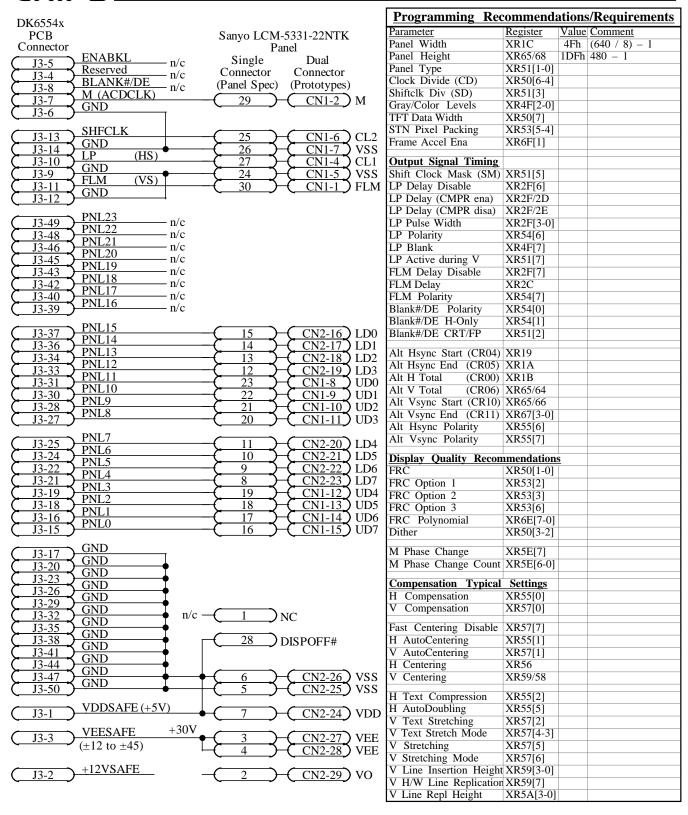

| Monochrome 16 Gray-Level EL                                                                                                                                                                                                                                                                      | 185<br>186<br>187<br>188<br>189<br>190<br>191<br>192 | Color STN DD - Kyocera KCL6448 Color STN DD - Hitachi LMG9720XUFC. Color STN DD - Sharp LM64C08P Color STN DD - Sanyo LCM5331-22NTK Color STN DD - Hitachi LMG9721XUFC. Color STN DD - Tosh. TLX-8062S-C3X Color STN DD - Opt DMF-50351NC-FW  Electrical Specifications  Reference Clock Timing Clock Generator Timing Reset Timing Local Bus Clock Timing Local Bus '2x' Clock Synch Timing Local Bus Input Setup & Hold Timing Local Bus Output Valid Timing | 234<br>235<br>236<br>237<br>238<br>239<br>240<br>243<br>244<br>245<br>246<br>246<br>247<br>248 |

| Application Schematics  ISA Bus Interface                                                                                                                                                                                                                                                        | 210<br>211<br>212<br>213                             | Local Output Float Delay Timing                                                                                                                                                                                                                                                                                                                                                                                                                                | 249<br>251<br>252<br>253<br>255<br>256<br>257<br>257                                           |

|                                                                                                                                                                                                                                                                                                  |                                                      | CRT Output Signal Timing PC Video Timing Panel Output Signal Timing                                                                                                                                                                                                                                                                                                                                                                                            | 258                                                                                            |

|                                                                                                                                                                                                                                                                                                  |                                                      | Mechanical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                      | 261                                                                                            |

|                                                                                                                                                                                                                                                                                                  |                                                      | Plastic 208-PFP Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                             | 261                                                                                            |

## **Introduction / Overview**

The 65540 / 545 High Performance Flat Panel / CRT Controllers initiate a family of 208-pin, high performance solutions for full-featured notebook / sub-notebook and other portable applications that require the highest graphics performance available. The 65545 is pin-to-pin compatible with the 65540 and adds a sophisticated graphics hardware engine for Bit Block Transfer (BitBLT), line drawing, hardware cursor, and other functions intensively used in Graphical User Interfaces (GUIs) such as Microsoft Windows<sup>TM</sup>. The 65540 and 65545 also use the same video BIOS, offering the system manufacturer a wide range of price / performance points while minimizing overhead for system integration and improving time-to-market. following table indicates feature differences between the 65540 and 65545:

| Features                        | 65540    | 65545 |

|---------------------------------|----------|-------|

| Support for all flat panels     | <b>√</b> | ✓     |

| VESA Local Bus / 16-bit ISA Bus | <b>\</b> | ✓     |

| 32-bit PCI Bus                  |          | ✓     |

| Linear Addressing               | <b>\</b> | ✓     |

| Hardware Accelerator            |          | ✓     |

| Hardware Cursor                 |          | ✓     |

| Pin Compatible                  | <b>√</b> | 1     |

| BIOS Compatible                 | <b>√</b> | 1     |

The 65540 / 545 family achieves superior performance through direct connection to system processor buses up to 32-bits in width. When combined with CHIPS' advanced linear acceleration software driver technology, these devices exhibit exceptional performance compared with devices of similar architecture. The 65540 / 545 architecture provides a fast throughput to video memory, maximizing the capability of today's powerful microprocessors to manipulate graphics operations. Based on the architecture of the 65540, the 65545 adds a powerful 32-bit graphics engine to offload graphics processing from the microprocessor for maximum performance.

Minimum chip-count, low-power graphics subsystem implementations are enabled through the high integration level of the 65540 / 545 family. These devices integrate the VGA-compatible graphics controller, true color RAMDAC, and dual PLL clock synthesizers. The entire graphics sub-

system can be implemented with a single 256Kx16 DRAM. The 32-bit local bus interface of the 65540 / 545 family eliminates external buffers.

For maximum performance, the 65540 / 545 supports an additional 256Kx16 DRAM, which provides a 32-bit video memory bus and additional display memory to support resolutions up to 1024x768 with 256 colors, 800x600 with 256 colors, and 640x480 with 16M colors. In addition, the 65540 / 545 family can support PC Video multimedia features while interfacing to a 32-bit local bus and one MByte of video memory.

The 65540 / 545 family supports a wide variety of monochrome and color Single-Panel, Single-Drive (SS) and Dual-Panel, Dual Drive (DD) passive STN and active matrix TFT / MIM LCD, EL, and plasma panels. The 65540 / 545 family supports panel resolutions of 800x600, 1024x768, and 1280x1024. For monochrome panels, up to 64 gray scales are supported. Up to 226,981 different colors can be displayed on passive STN LCDs and up to 16M colors on 24-bit active matrix LCDs using the 65540 / 545 controllers.

The 65540 / 545 family offers a variety of programmable features to optimize display quality. For text modes which do not fill all 480 lines of a standard VGA panel, the 65540 / 545 provides tall font stretching in the hardware. Fast vertical centering and programmable vertical stretching in graphics modes offer more options for handling modes with less than 480 lines. Three selectable color-to-grayscale reduction techniques SMARTMAP<sup>TM</sup> are available for improving the viewability of color applications on monochrome panels. CHIPS' polynomial FRC algorithm reduces panel flicker on a wider range of panel types with a single setting for a particular panel type.

The 65540 / 545 employs a variety of advanced power management features to reduce power consumption of the display subsystem and extend battery life. The 65540 / 545's internal logic, memory interface, bus interface, and flat panel interfaces can be independently configured to operate at either 3.3 V or 5.0 V. The 65540 / 545 is optimized for minimum power consumption during normal operation and provides two power-saving modes - Panel Off and Standby. During Panel Off mode, the 65540 / 545 turns off the flat panel while

the VGA subsystem remains active. The palette may also be automatically shut off during Panel Off mode to further reduce power consumption. During Standby mode, the 65540 / 545 suspends all CPU, memory and display activities. In this mode, the 65540 / 545 places the DRAM in self-refresh mode and the 65540 / 545 reference input clock can be turned off. The 65540 / 545 also provides a programmable activity timer which monitors VGA activity. After all display activity ceases, the timer will automatically shut down the panel by either disabling the backlight or putting the 65540 / 545 in Panel Off mode.

The 65540 / 545 is fully compatible with the VGA graphics standard at the register, gate, and BIOS levels. The 65540 / 545 provides full backwards compatibility with the EGA and CGA graphics standards without using NMIs. CHIPS and third-party vendors supply fully VGA-compatible BIOS, end-user utilities and drivers for common application programs (e.g., Microsoft Windows<sup>TM</sup>, OS/2, WordPerfect, Lotus, etc.). CHIPS' drivers for Windows include a Big Cursor (to increase the cursor's legibility on monochrome flat panels) and panning / scrolling capability (to increase performance).

#### MINIMUM CHIP COUNT / BOARD SPACE

The 65540 / 545 provides a minimum chip count / board space, yet highly flexible VGA subsystem. The 65540 / 545 integrates a high-performance VGA flat panel / CRT controller, industry-standard RAMDAC, clock synthesizer, monitor sense circuitry and an activity timer in a 208-pin plastic flat pack package. In its minimum configuration, the 65540 / 545 requires only a single 256Kx16 DRAM, such that a complete VGA subsystem for motherboard applications can be implemented with just two ICs. This configuration consumes less than 2 square inches (1290 sq mm) of board space and is capable of supporting simultaneous flat panel / CRT display requirements while directly interfacing to a 32-bit local bus. As an option, a second memory chip may be implemented to increase performance (via a 32-bit data path to display memory) and support graphics modes which require more than 512 KBytes of display memory. No external buffers or glue logic are required for the 65540 / 545's bus interface, memory interface, or panel interface. The 65540 / 545 employs separate address and data buses with sufficient drive capability such that the bus can be driven directly. The 65540 / 545 also provides up to 24 bits of panel data with sufficient drive capability such that virtually all flat panels can be driven directly.

#### **DISPLAY MEMORY INTERFACE**

The 65540 / 545 supports multiple display memory configurations, providing the OEM with the flexibility to use the same VGA controller in several designs with differing cost, power consumption and performance criteria. The 65540 / 545 supports the following display memory configurations:

- One 256Kx16 DRAM (512 KBytes)

- Two 256Kx16 DRAMs (1 MBytes)

- Four 256Kx4 DRAMs (512 KBytes)

Performance is significantly improved when the 65540 / 545 is configured with a 32-bit data path to display memory, which is accomplished by using two 256Kx16 DRAMs. Two 256Kx16 DRAMs support all standard, Super, and Extended VGA resolutions up to 1024x768 256 colors as well as "high" 16bpp color and "true" 24bpp color modes. The table on the following page summarizes the display capabilities of the 65540 / 545.

Display memory control signals are derived from the integrated clock synthesizer's memory clock. The 65540 / 545 serves as a DRAM controller for the system's display memory. It handles DRAM refresh, fetches data from display memory for display refresh, interfaces the CPU to display memory, and supplies all necessary DRAM control signals.

The 65540 / 545 supports 'two-CAS / one-WE' and 'one-CAS / two-WE' 256Kx16 DRAMs. The 65540 / 545 supports the self-refresh features of 256Kx16 DRAMs and certain 256Kx4 DRAMs during Standby mode, enabling the 65540 / 545 to be powered down completely during suspend/resume operation.

## 65540 / 545 Display Capabilities

| CRT Mode<br>Resolution Color <sup>4</sup> |             | Mono LCD<br>Gray Scales <sup>4</sup> | DD STN LCD<br>Colors 2, 3, 4 | 9-Bit TFT LCD<br>Colors 1, 2, 3, 4 | Video<br>Memory | Simultaneous<br>Display |

|-------------------------------------------|-------------|--------------------------------------|------------------------------|------------------------------------|-----------------|-------------------------|

| 320x200                                   | 256 / 256K† | 61 / 61                              | 256 / 226,981                | 256 / 185,193                      | 512KB           | Yes                     |

| 640x480                                   | 16 / 256K†  | 16 / 61                              | 16 / 226,981                 | 16 / 185,193                       | 512KB           | Yes                     |

| 640x480                                   | 256 / 256K† | 61 / 61                              | 256 / 226,981                | 256 / 185,193                      | 512KB           | Yes                     |

| 800x600                                   | 16 / 256K†  | 16 / 61                              | 16 / 226,981                 | 16 / 185,193                       | 512KB           | Yes with 1MB            |

| 800x600                                   | 256 / 256K† | 61 / 61                              | 256 / 226,981                | 256 / 185,193                      | 512KB           | Yes with 1MB            |

| 1024x768                                  | 16 / 256K†  | 16 / 61                              | 16 / 226,981                 | 16 / 185,193                       | 512KB           | Yes with 1MB            |

| 1024x768                                  | 256 / 256K† | 61 / 61                              | 256 / 226,981                | 256 / 185,193                      | 1MB             | Yes                     |

| 1280x1024                                 | 16 / 256K†  | 16 / 61                              | n/a                          | n/a                                | 1MB             | n/a                     |

#### Notes:

- 1 Larger color palettes and simultaneous colors can be displayed on 12-bit, 18-bit, and 24-bit TFT panels via the 65540 / 545 video input port

- 2 Includes dithering

- 3 Includes frame rate control

- 4 Colors are described as number of simultaneous on-screen colors and number of unique colors available in the color palette

- † 256K colors assumes DAC output mode is set to 6 bits of R, G, & B. If DAC is set to 8-bit output mode, the number of available colors is 16M

#### **CPU BUS INTERFACE**

The 65540 / 545 provides a direct interface to:

- 32-bit VL-Bus

- 32-Bit 386/486 CPU local bus

- EISA/ISA (PC/AT) 16-bit bus

- PCI Bus (65545 only)

Strap options allow the user to configure the chip for the type of interface desired. Control signals for all interface types are integrated on chip. All operations necessary to ensure proper functioning in these various environments are handled in a fashion transparent to the CPU. These include internal decoding of all memory and I/O addresses, bus width translations, and generation of necessary control signals.

#### HIGH PERFORMANCE FEATURES

The 65540 / 545 includes a number of performance enhancement techniques including:

- Direct 32-bit local bus CPU support

- 32-bit interface to video memory

- Linearly addressable display memory

- 32-bit graphics hardware engine (65545 only)

- 64x64x2 hardware cursor (65545 only)

The 65540 /545 provides an optimized 32-bit path from 32-bit CPUs direct to the video memory. Running the 32-bit local bus of the 65540 / 545 at CPU speeds up to 33 MHz maximizes data throughput and drawing speed for today's powerful CPU architectures. Addressing pixels linearly maximizes the efficiency of software drivers, enabling the CPU to make the most use of the full 32-bit path through the 65540 / 545 controller. Software drivers optimized for linear addressing are available from CHIPS and improve performance up to 80% over standard software methods.

#### 65545 ACCELERATION

Several functions traditionally performed by software have been implemented in hardware in the 65545 to off load the CPU and further improve performance. Three-Operand BitBLT logic supports all 256 logical combinations of Source, Destination, and Pattern. All BitBLTs are executed up to 32-bits per cycle, maximizing the efficiency of memory accesses. A 32-bit color expansion engine allows the host CPU to transfer monochrome "maps" of color images over the system bus at high speeds to the 65545, which decodes the monochrome images into their color Line drawing is also accelerated with form. hardware assistance.

#### 65545 HARDWARE CURSOR

A programmable-size hardware cursor frees software from continuously generating the cursor image on the display. The 65545 supports four types of cursors:

32 x 32 x 2bpp (and/xor) 64 x 64 x 2bpp (and/xor) 64 x 64 x 2bpp (4-color) 128 x 128 x 1bpp (2-color)

The first two hardware cursor types indicated as 'and/xor' above follow the MS Windows<sup>TM</sup> AND/XOR cursor data plane structure which provides for two colors plus 'transparent' (background color) and 'inverted' (background color inverted). The last two types in the list above are also referred to as 'Pop-Ups' because they are typically used to implement pop-up menu capabilities. Hardware cursor / pop-up data is stored in display memory, allowing multiple cursor values to be stored and selected rapidly. The two or four colors specified by the values in the hardware cursor data arrays are stored in on-chip registers as high-color (5-6-5) values independent of the on-chip color lookup tables.

The hardware cursor can overlay either graphics or video data on a pixel by pixel basis. It may be positioned anywhere within screen resolutions up to 2048x2048 pixels. 64x64 'and/xor' cursors may also be optionally doubled in size to 128 pixels either horizontally and/or vertically by pixel replication.

Hardware cursor screen position, type, color, and base address of the cursor data array in display memory may be controlled via the 32-bit 'DR' extension registers.

#### PC VIDEO / OVERLAY SUPPORT

The 65540 / 545 allows up to 24 bits of external RGB video data to be input and merged with the internal VGA data stream. The 65540 / 545 supports two forms of video windowing: (i) color key input and (ii) X-Y window keying. The X-Y window key input can be used to position the live video window coordinates. The 65540 / 545 can be used in conjunction with Chips and Technologies, Inc. PC Video products to provide portable multimedia solutions.

#### **DISPLAY INTERFACE**

The 65540 / 545 is designed to support a wide range of flat panel and CRT displays of all different types and resolutions.

#### **Flat Panel Displays**

The 65540 / 545 supports all flat panel display technologies including plasma, electroluminescent (EL) and liquid crystal displays (LCD). LCD panel interfaces are provided for single panel-single drive (SS) and dual panel-dual drive (DD) configurations. A single panel sequences data similar to a CRT (i.e., sequentially from one area of video memory). In contrast, a dual panel requires video data to be provided alternating from two separate areas of video memory. In addition, a dual drive panel requires the data from the two areas to be provided to the panel simultaneously. Due to its integrated frame buffer and 24-data-line panel interface, the 65540 / 545 supports all panels directly. Support for LCD-DD panels does not require external hardware such as a frame buffer. Support for highresolution, 'high color' flat panels also does not require additional components. The 65540 / 545 handles display data sequencing transparently to applications software, providing full compatibility on both CRT and flat panel displays.

| 9-bit<br>'512-Color'  | 12-bit<br>'4096-Color'        | Dither | FRC |

|-----------------------|-------------------------------|--------|-----|

| 512 (8 <sup>3</sup> ) | $4096 (16^3)$                 | No     | No  |

| $3,375 (15^3)$        | $29,791(31^3)$                | No     | Yes |

| $24,389(29^3)$        | 226,981 (61 <sup>3</sup> )    | Yes    | No  |

| $185,193(57^3)$       | 1,771,561 (121 <sup>3</sup> ) | Yes    | Yes |

There is currently no standard interface for flat panel displays. Interface signals and timing requirements vary between panel technologies and suppliers. The 65540 / 545 provides register programmable features to allow interfacing to the widest possible range of flat panel displays. The 65540 / 545 provides a direct interface to panels from vendors such as Sharp, Sanyo, Epson, Seiko Instruments, Oki, Toshiba, Hitachi, Fujitsu, NEC, Matsushita/Panasonic, and Planar.

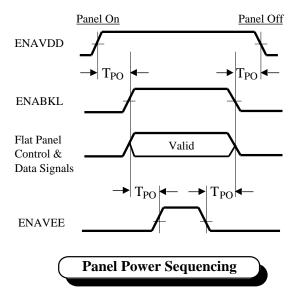

## PANEL POWER SEQUENCING

Flat panel displays are extremely sensitive to conditions where full biasing voltage VEE is applied to the liquid crystal material without enabling the control and data signals to the panel. This results in severe damage to the panel and may disable the panel permanently. The 65540 / 545 provides a simple and elegant method to sequence power to the flat panel display during various modes of operation to conserve power and provide safe operation to the flat panel. The 65540 / 545 provides three pins

called ENAVEE, ENAVDD and ENABKL to regulate the LCD Bias Voltage (VEE), the driver electronics logic voltage (VDD), and the backlight voltage (BKL) to provide intelligent power sequencing to the panel. The timing diagram below illustrates the power sequencing cycle. In the 65540 / 545, the power on/off delay time (TPO) is programmable (with a default of 32 mS).

The 65540 / 545 initiates a 'panel off' sequence if the STNDBY# input is asserted (low), or if XR52 bit-4 is set to a '1' putting the chip into STNDBY mode. The 65540 / 545 also initiates a 'panel off' sequence if the chip is programmed to enter 'panel off' mode (by setting extension register XR52 bit-3=1), or if the 'Display Type' is programmed to 'CRT' (extension register XR51 bit-2 transitions from '1' to '0'). The 65540 / 545 initiates a 'panel on' sequence if the STNDBY# input is high and the chip is programmed to 'panel on' (XR52 bit-3 transitions from a '1' to '0') and 'flat panel display' (XR51 bit-2 is set to '1').

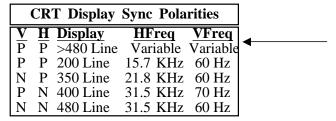

#### **CRT Displays**

The 65540 / 545 supports high resolution fixed frequency and variable frequency analog monitors in interlaced and non-interlaced modes of operation. Digital monitor support is also built in.

The 65540 / 545 supports resolutions up to 1024x768 256 colors, 800x600 256 colors or 640x480 16,777,216 colors in 1 MByte display memory configurations, 1024x768 16 colors, 800x600 256 colors in 512 KBytes display memory configurations. The tables starting on the following page list all 65540 / 545 CRT monitor video modes.

## Supported Video Modes - VGA Standard

|        |              |        |         |      |            |                 | Horizontal | Vertical  |        |       |

|--------|--------------|--------|---------|------|------------|-----------------|------------|-----------|--------|-------|

| Mode#  | Display      |        | Text    | Font | Pixel      | <b>DotClock</b> | Frequency  | Frequency | Video  |       |

| (Hex)  | Mode         | Colors | Display | Size | Resolution | (MHz) †         | (KHz)      | (Hz)      | Memory | CRT   |

| 0, 1   | Text         | 16     | 40 x 25 | 8x8  | 360x400    | 28.322          | 31.5       | 70        | 256 KB | A,B,C |

| 0*, 1* |              |        | 40 x 25 | 8x14 | 320x350    | 25.175          |            |           |        |       |

| 0+, 1+ |              |        | 40 x 25 | 8x8  | 320x200    | 25.175          |            |           |        |       |

| 2, 3   | Text         | 16     | 80 x 25 | 9x16 | 720x400    | 28.322          | 31.5       | 70        | 256 KB | A,B,C |

| 2*, 3* |              |        | 80 x 25 | 8x14 | 640x350    | 25.175          |            |           |        |       |

| 2+, 3+ |              |        | 80 x 25 | 8x8  | 640x200    | 25.175          |            |           |        |       |

| 4      | Graphics     | 4      | 40 x 25 | 8x8  | 320x200    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

| 5      | Graphics     | 4      | 40 x 25 | 8x8  | 320x200    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

| 6      | Graphics     | 2      | 80 x 25 | 8x8  | 640x200    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

| 7      | Text         | Mono   | 80 x 25 | 9x16 | 720x400    | 28.322          | 31.5       | 70        | 256 KB | A,B,C |

| 7+     |              |        | 80 x 25 | 9x14 | 720x350    |                 |            |           |        |       |

| D      | Planar       | 16     | 40 x 25 | 8x8  | 320x200    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

| Е      | Planar       | 16     | 80 x 25 | 8x8  | 640x200    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

| F      | Planar       | Mono   | 80 x 25 | 8x14 | 640x350    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

| 10     | Planar       | 16     | 80 x 25 | 8x14 | 640x350    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

| 11     | Planar       | 2      | 80 x 30 | 8x16 | 640x480    | 25.175          | 31.5       | 60        | 256 KB | A,B,C |

| 12     | Planar       | 16     | 80 x 30 | 8x16 | 640x480    | 25.175          | 31.5       | 60        | 256 KB | A,B,C |

| 13     | Packed Pixel | 256    | 40 x 25 | 8x8  | 320x200    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

Note: • All of the above VGA standard modes are supported directly in the 65548 BIOS (both 32K and 40K BIOS versions).

- All of the above VGA standard modes are supported at both 3.3V and 5V.

- All VGA modes using 25.175 MHz and 28.322 MHz can also be supported using 32 MHz and 36 MHz respectively.

In this case, the horizontal frequency becomes 40.000 KHz and the vertical frequency becomes 89 Hz.

(see XR33 bit-7 "ISO Mode Control" for selection of VGA dot clock frequencies)

Note: Not all above resolutions can be supported at both 3.3V and 5V.

#### CRT Codes:

- A PS/2 fixed frequency analog CRT monitor or equivalent (31.5 / 35.5 KHz Horizontal Frequency Specification)

- B Multi-Frequency CRT monitor (37.5 KHz Minimum Horizontal Frequency Specification) (NEC MultiSync 3D or equivalent)

- C Multi-Frequency High-Performance CRT Monitor (48.5 KHz Min H Freq Specification) (Nanao Flexscan 9070s, MultiSync 5D, or equivalent)

<sup>†</sup> Refer to Electrical Specifications section for maximum clock frequencies for 5V and 3.3V operation.

## **Supported Video Modes - Extended Resolution**

|         |              |        |          |             |            |                 | Horizontal | Vertical  |        |       |

|---------|--------------|--------|----------|-------------|------------|-----------------|------------|-----------|--------|-------|

| Mode#   | Display      |        | Text     | <b>Font</b> | Pixel      | <b>DotClock</b> | Frequency  | Frequency | Video  |       |

| (Hex)   | Mode         | Colors | Display  | Size        | Resolution | (MHz) †         | (KHz)      | (Hz)      | Memory | CRT   |

| 20      | 4 bit Linear | 16     | 80 x 30  | 8x16        | 640x480    | 25.175          | 31.5       | 60        | 512 KB | A,B,C |

| 22      | 4 bit Linear | 16     | 100 x 37 | 8x16        | 800x600    | 40.000          | 37.5       | 60        | 512 KB | В,С   |

| 24      | 4 bit Linear | 16     | 128 x 48 | 8x16        | 1024x768   | 65.000          | 48.5       | 60        | 512 KB | C     |

| 24 I    | 4 bit Linear | 16     | 128 x 48 | 8x16        | 1024x768   | 44.900          | 35.5       | 43        | 512 KB | В,С   |

| 28I     | 4 bit Linear | 16     | 128 x 48 | 8x16        | 1280x1024  | 65.000          | 42.5       | 39        | 1 MB   | С     |

| 30      | 8 bit Linear | 256    | 80 x 30  | 8x16        | 640x480    | 25.175          | 31.5       | 60        | 512 KB | A,B,C |

| 32      | 8 bit Linear | 256    | 100 x 37 | 8x16        | 800x600    | 40.000          | 37.5       | 60        | 512 KB | В,С   |

| 34      | 8 bit Linear | 256    | 128 x 48 | 8x16        | 1024x768   | 65.000          | 48.5       | 60        | 1 MB   | С     |

| 34 I    | 8 bit Linear | 256    | 128 x 48 | 8x16        | 1024x768   | 44.900          | 35.5       | 43        | 1 MB   | В,С   |

| 40      | 15bit Linear | 32K    | 80 x 30  | 8x16        | 640x480    | 50.350          | 31.5       | 60        | 1 MB   | A,B,C |

| 41      | 16bit Linear | 64K    | 80 x 30  | 8x16        | 640x480    | 50.350          | 31.5       | 60        | 1 MB   | A,B,C |

| 50      | 24bit Linear | 16M    | 80 x 30  | 8x16        | 640x480    | 65.000          | 27.1       | 51.6      | 1 MB   | В,С   |

| 60      | Text         | 16     | 132 x 25 | 8x16        | 1056x400   | 40.000          | 30.5       | 68        | 256 KB | A,B,C |

| 61      | Text         | 16     | 132 x 50 | 8x16        | 1056x400   | 40.000          | 30.5       | 68        | 256 KB | A,B,C |

| 6A, 70  | Planar       | 16     | 100 x 37 | 8x16        | 800x600    | 40.000          | 38.0       | 60        | 256 KB | B,C   |

| 72,75   | Planar       | 16     | 128 x 48 | 8x16        | 1024x768   | 65.000          | 48.5       | 60        | 512 KB | C     |

| 72, 75I | Planar       | 16     | 128 x 48 | 8x16        | 1024x768   | 44.900          | 35.5       | 43        | 512 KB | B,C   |

| 78      | Packed Pixel | 16     | 80 x 25  | 8x16        | 640x400    | 25.175          | 31.5       | 70        | 256 KB | A,B,C |

| 79      | Packed Pixel | 256    | 80 x 30  | 8x16        | 640x480    | 25.175          | 31.5       | 60        | 512 KB | A,B,C |

| 7C      | Packed Pixel | 256    | 100 x 37 | 8x16        | 800x600    | 40.000          | 37.5       | 60        | 512 KB | В,С   |

| 7E      | Packed Pixel | 256    | 128 x 48 | 8x16        | 1024x768   | 65.000          | 48.5       | 60        | 1 MB   | С     |

| 7E I    | Packed Pixel | 256    | 128 x 48 | 8x16        | 1024x768   | 44.900          | 35.5       | 43        | 1 MB   | В,С   |

| 76 I    | 4 bit Planar | 16     | 128 x 48 | 8x16        | 1280x1024  | 65.000          | 42.5       | 39        | 1 MB   | С     |

Note: Support for the modes in the above table is included directly in the BIOS (both 32K and 40K versions). The "I" in the mode # column indicates "Interlaced".

## **Supported Video Modes - High Refresh**

|        |              |        |          |             |            |                 | Horizontal | Vertical  |        |     |

|--------|--------------|--------|----------|-------------|------------|-----------------|------------|-----------|--------|-----|

| Mode#  | Display      |        | Text     | <b>Font</b> | Pixel      | <b>DotClock</b> | Frequency  | Frequency | Video  |     |

| (Hex)  | Mode         | Colors | Display  | Size        | Resolution | (MHz) †         | (KHz)      | (Hz)      | Memory | CRT |

| 12*    | Planar       | 16     | 80 x 30  | 8x16        | 640x480    | 31.500          | 37.5       | 75        | 256 KB | В,С |

| 30     | 8 bit Linear | 256    | 80 x 30  | 8x16        | 640x480    | 31.500          | 37.5       | 75        | 256 KB | С   |

| 79     | Packed Pixel | 256    | 80 x 30  | 8x16        | 640x480    | 31.500          | 37.5       | 75        | 512 KB | С   |

| 6A, 70 | Planar       | 16     | 100 x 37 | 8x16        | 800x600    | 49.500          | 46.9       | 75        | 512 KB | С   |

| 32     | 8 bit Linear | 256    | 100 x 37 | 8x16        | 800x600    | 49.500          | 46.9       | 75        | 1 MB   | С   |

| 7C     | Packed Pixel | 256    | 100 x 37 | 8x16        | 800x600    | 49.500          | 46.9       | 75        | 1 MB   | С   |

Note: Not all above resolutions can be supported at both 3.3V and 5V.

#### CRT Codes:

- A PS/2 fixed frequency analog CRT monitor or equivalent (31.5 / 35.5 KHz Horizontal Frequency Specification)

- B Multi-Frequency CRT monitor (37.5 KHz Minimum Horizontal Frequency Specification) (NEC MultiSync 3D or equivalent)

- C Multi-Frequency High-Performance CRT Monitor (48.5 KHz Min H Freq Specification) (Nanao Flexscan 9070s, MultiSync 5D, or equivalent)

<sup>†</sup> Refer to Electrical Specifications section for maximum clock frequencies for 5V and 3.3V operation.

#### Simultaneous Flat Panel / CRT Display

The 65540 / 545 provides simultaneous display operation with Multi-Sync variable frequency or PS/2 fixed frequency CRT monitors and single panel-single drive LCDs (LCD-SS), dual panel-dual drive LCDs (LCD-DD), and plasma and EL panels (which employ single panel-single drive interfaces). Single drive panels sequence data in the same manner as CRTs, so the 65540 / 545 provides simultaneous CRT display with LCD-SS, Plasma, and EL panels by driving the panels with CRT timing. LCD-DD panels require video data alternating between two separate locations in memory. In addition, a dual drive panel requires data from both locations simultaneously. A framestore area, also called the frame buffer, is required to achieve this operation. The 65540 / 545 innovative architecture implements the frame buffer in an unused area of display memory, reducing chip count and subsystem cost. As an option, an extra 16-bit wide DRAM can be used as an external frame buffer, improving performance while in simultaneous flat panel/CRT modes. The 65540 / 545 provides simultaneous display with monochrome and color LCD-DD panels with a single 256Kx16 DRAM.

#### **DISPLAY ENHANCEMENT FEATURES**

Display quality is one of the most important features for the success of any flat panel-based system. The 65540 / 545 provides many features to enhance the flat panel display quality.

#### "TRUE-GRAY" Gray Scale Algorithm

A proprietary polynomial-based Frame Rate Control (FRC) and dithering algorithm in the 65540 / 545's hardware generates a maximum of 61 gray levels on monochrome panels. The FRC technique simulates a maximum of 16 gray levels on monochrome panels by turning the pixels on and off over several frames in time. The dithering technique increases the number of gray scales from 16 to 61 by altering the pattern of gray scales in adjacent pixels. The persistence (response time) of the pixels varies among panel manufacturers and models. By re-programming the polynomial (an 8bit value in Extension Register XR6E) while viewing the display, the FRC algorithm can be adjusted to match the persistence of the particular panel without increasing the panel's vertical refresh rate. With this technique, the 65540 / 545 produces up to 61 flicker-free gray scales on the latest fast response "mouse quick" film-compensated monochrome STN LCDs. The alternate method of reducing flicker -- increasing the panel's vertical

refresh rate -- has several drawbacks. As the vertical refresh rate increases, panel power consumption increases, ghosting (cross-talk) increases, and contrast decreases. CHIPS' polynomial FRC gray scale algorithm reduces flicker without increasing the vertical refresh rate.

#### **RGB Color To Gray Scale Reduction**

The 24 bits of color palette data from the VGA standard color lookup table (CLUT) are reduced to 6 bits for 64 gray scales via one of three selectable RGB color to gray scale reduction techniques:

- 1) NTSC Weighting: 5/16 Red 9/16 Green 2/16 Blue

- 2) Equal Weighting: 5/16 Red 6/16 Green 5/16 Blue

- 3) Green Only: 6 bits of Green only

NTSC is the most common weighting, which is used in television broadcasting. Equal weighting increases the weighting for Blue, which is useful for Applications such as Microsoft Windows 3.1 which often uses Blue for background colors. Green-Only is useful for replicating on a flat panel the display of software optimized for IBM's monochrome monitors which use the six green bits of palette data.

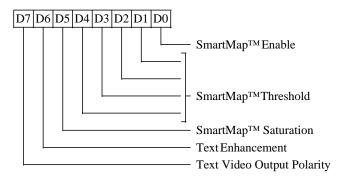

## $SmartMap^{TM}$

SmartMap<sup>TM</sup> is a proprietary feature that can be invoked to intelligently map colors to gray levels in text mode. SmartMap<sup>TM</sup> improves the legibility of flat panel displays by solving a common problem:

Most application programs are optimized for color CRT monitors using multiple colors. For example, a word processor might use a blue background with white characters for normal text, underlined text could be displayed in green, italicized text in yellow, and so on. This variety of colors, which is quite distinct on a color CRT monitor, can be illegible on a monochrome flat panel display if the colors are mapped to adjacent gray scale values. In the example, underlined and italicized text would be illegible if yellow is mapped to gray scale 4, green to gray scale 6 with the blue background mapped to gray scale 5.

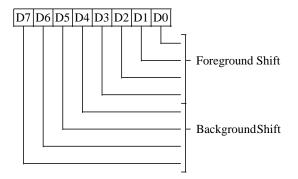

SmartMap<sup>TM</sup> compares and adjusts foreground and background grayscale values to produce adequate display contrast on flat panel displays. The minimum contrast value and the foreground / background grayscale adjustment values are programmed in the 65540 / 545's Extension Registers. This feature can be disabled if desired.

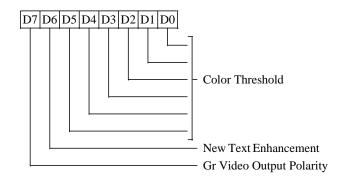

#### **Text Enhancement**

Text Enhancement is another feature of the 65540 / 545 that improves image quality on flat panel displays. When enabled, the Text Enhancement feature displays Dim White as Bright White, thereby optimizing the contrast level on flat panels. Text Enhancement can be enabled and disabled by changing a bit in one of the Extension Registers.

#### **Vertical & Horizontal Compensation**

Vertical & Horizontal Compensation are programmable features that adjust the display to completely fill the flat panel display. Vertical Compensation increases the useable display area when running lower resolution software on a higher resolution panel. Unlike CRT monitors, flat panels have a fixed number of scan lines (e.g., 200, 400, 480 or 768 lines). Lower resolution software displayed on a higher resolution panel only partially fills the useable display area. For instance, 350-line EGA software displayed on a 480-line panel would leave 130 blank lines at the bottom of the display and 400-line VGA text or Mode 13 images would leave 80 blank lines at the bottom. The 65540 / 545 offers the following Vertical Compensation techniques to increase the useable screen area:

Vertical Centering displays text or graphics images in the center of the flat panel, with a border of unused area at the top and bottom of the display. Automatic Vertical Centering automatically adjusts the Display Start address such that the unused area at the top of the display equals the unused area at the bottom. Non-Automatic Vertical Centering enables the Display Start address to be set (by programming the Extension Registers) such that text or graphics images can be positioned anywhere on the display.

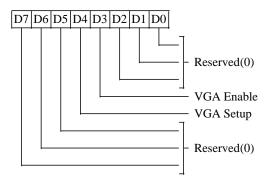

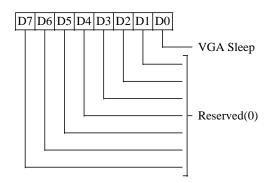

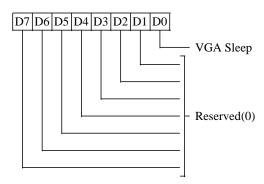

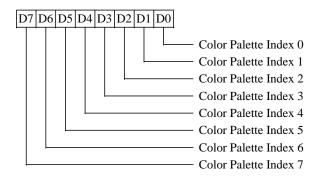

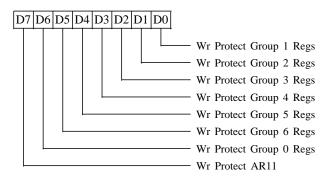

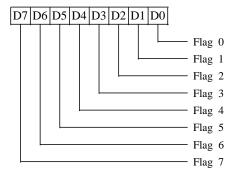

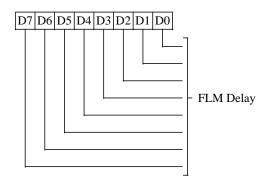

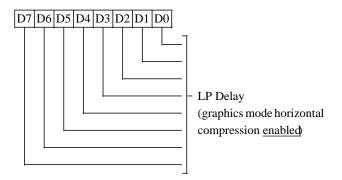

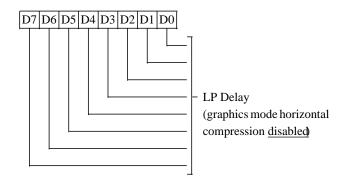

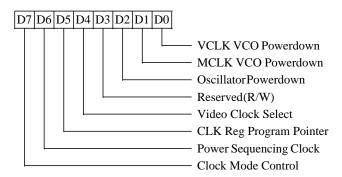

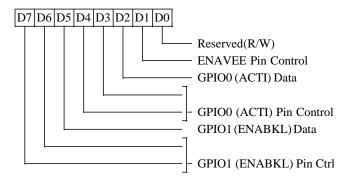

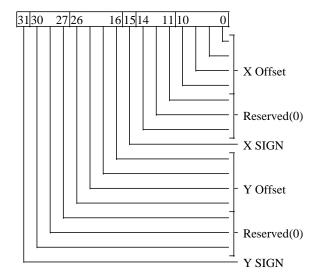

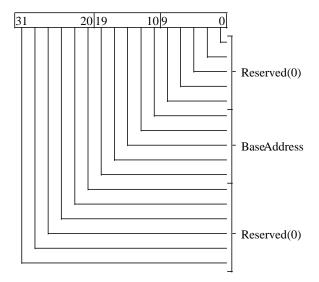

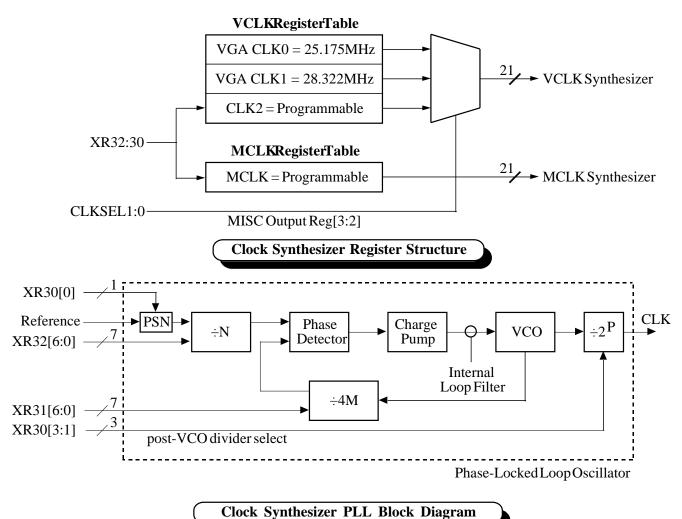

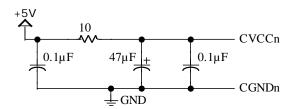

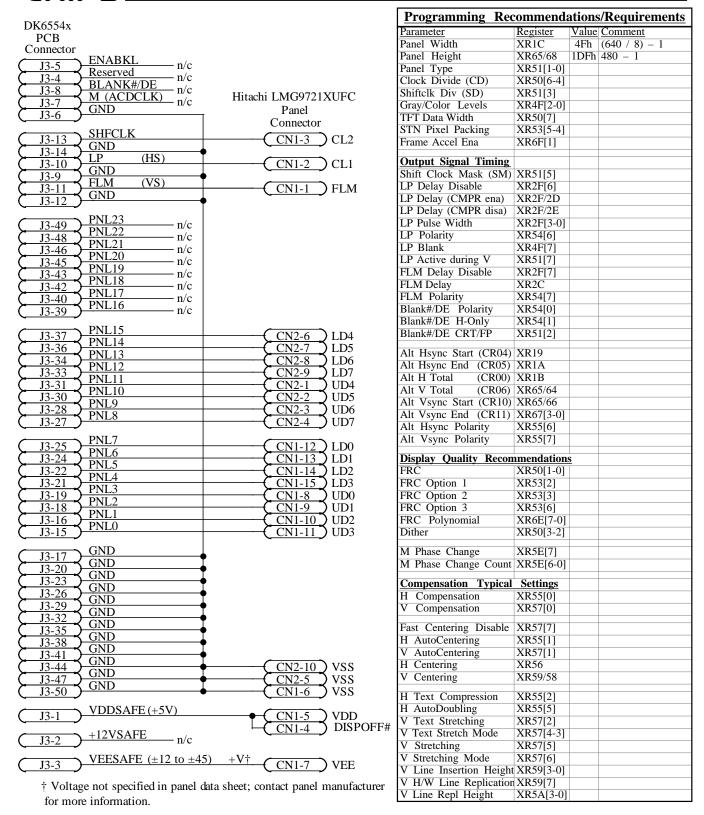

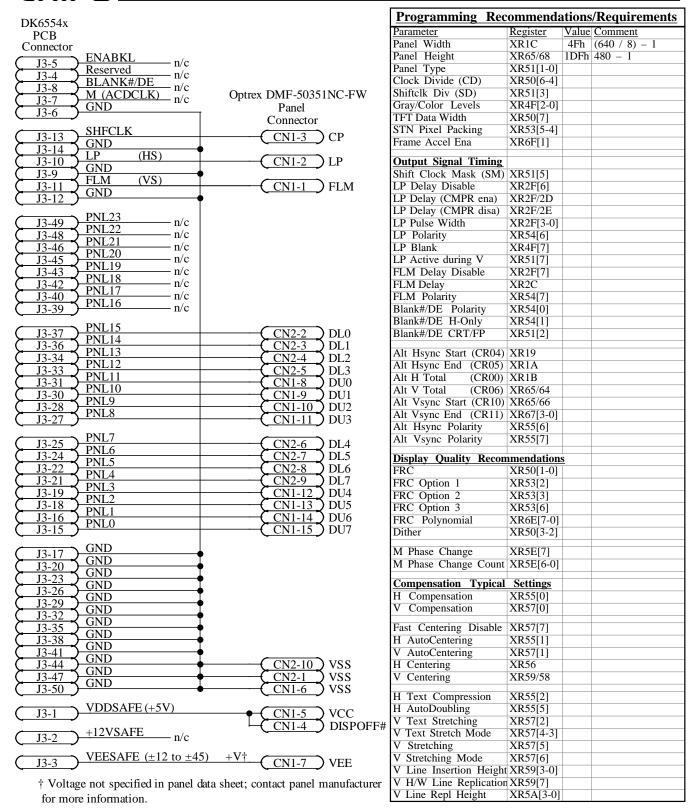

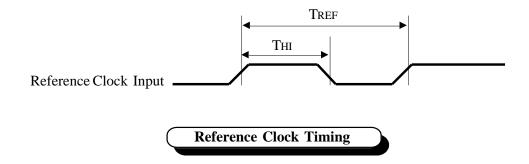

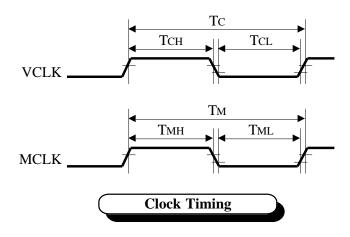

Line replication (referred to as "stretching") duplicates every Nth display line (where N is programmable), thus stretching text characters and graphic images an adjustable amount. The display can be stretched to completely fill the flat panel area. Double scanning, a form of line replication where every line is replicated, is useful for running 200-line software on a 400-line panel or 480-line software on a 1024-line panel.